1 引言

移动操作 或移动计算(mobile computing)原是通讯领域的研究方向,随着数字无线通信技术和嵌入式计算技术的发展、应用与融合,移动操作已逐步成为嵌入式系统中很具发展潜力的一个领域[1]。 SoC (System on a Chip)是嵌入式系统的研究和开发热点[2],其运用现代计算机和微电子学的高技术,实现单片系统集成,减小了体积、提高了运行效率、增强了可靠性、降低了功耗、减少了成本,被称作嵌入式系统应用的理想结构。移动操作和SoC二者的结合开拓出了嵌入式系统研究与应用的新天地。为了解释移动操作SoC的应用,这里举一个例子,如图1所示。

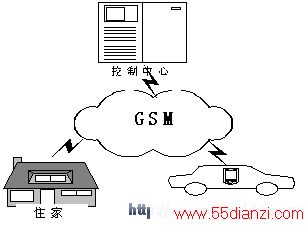

图1 一种移动操作SoC的工作示意图

在图1中,移动操作SoC被设置在 汽车 上,它通过GSM通信网络和控制中心、住家建立通信联系。车主能够通过汽车上的移动操作SoC控制住家的各种家用电器设备,如在回家的路上可以启动电饭煲和微波炉;也可以向控制中心发出咨询和数据提取信息。同时,车主可以通过移动操作SoC对住家内设置的保安系统、防火系统进行检查,及时发现问题,并向控制中心求助。另一方面,住家的安全问题信息也可以通过GSM传递给控制中心和车主,以便及时采取措施。

当车主在住家时,汽车上的移动操作SoC和车上的防盗系统连接,在发生汽车被盗事件时,及时向车主和控制中心报警。

由此可见,在移动通信日益发达的今天,移动操作SoC必将成为嵌入式系统应用研究新的热点之一,有着广阔的发展空间。

2 移动操作SoC的结构

作为SoC在移动通信控制的分支,移动操作SoC和一般的SoC在设计上是相似的。作为一个系统的核心,SoC要完成运行、操作或控制功能,必须有相应的组件配合。而多数组件,尤其是外部组件在SoC内都要有一个对应的控制器。所以,为了实现应用对象操作,SoC要设计相当数量的组件控制器。组件控制器的设计,对SoC而言就是一些IP(Intellectual Property)组件的设计。由于可编程器件PLD具有简单易学、修改方便的特点,常常被用来作为设计 IP组件 的硬件支撑。

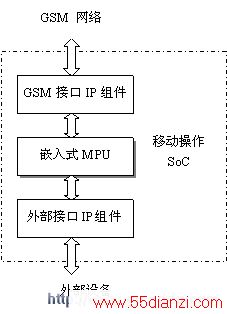

移动操作SoC的基本结构见图2。在移动操作SoC中,核心是嵌入式微处理器MPU。实际上,多数的MPU和是由MPU或PLD设计与开发公司提供的,如MCS51系列的NIOS和32位的ARM系列MPU核,分别由ALTEra和Arm公司提供给用户[3]。

图2 移动操作SoC的基本结构

从用户的角度来看,进行SoC设计的主要工作是IP组件的设计,以及系统的连接。尽管SoC的IP核分为硬核、软核、固核,对于非专业集成电路设计的用户来说,多数采用基于PLD的设计方法。也就是软硬结合的IP固核设计。

从图2可以看出,移动操作SoC的IP设计主要包括两个部分:GSM接口IP组件和外部接口IP组件。其中GSM接口IP组件建立移动操作SoC和GSM网络的通信联系和相应的数据变换;外部接口IP组件则负责SoC与外部设备间的数据联系,并对某些外部设备器驱动控制作用。

相对来说,外部接口IP组件包含的内容更丰富。因为,这类IP组件对应的外部设备范围较广,而GSM接口IP组件只对应GSM网络。对一个嵌入了移动操作SoC的电子产品而言,常用的外部设备包括键盘、显示、外部存储器和鸣响器件等。无论是键盘、显示、外部存储器,还是鸣响器件,其相应的IP组件都具有一定驱动控制功能。

基于PLD设计SoC的IP组件是较常用的方法。目前,应用较多PLD器件是FPGA和CPLD,本文中介绍的IP组件设计是在基于VHDL编程的FPGA上完成的[4]。

3 移动操作SoC的IP组件设计

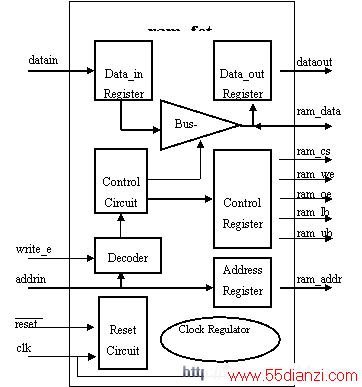

外部接口IP组件是移动操作SoC应用中常用且范围较广的IP组件。外部数据存储器是SoC的一种常用外部设备。为了实现SoC对外部数据存储器的高效管理,要设计一个外部数据存储器IP组件。这个组件被命名为ram_fct。外部数据存储器IP组件结构可参考图3。

对照图2,图3中的ram_fct是外部数据存储器的IP组件,处于外部数据存储器和嵌入式MPU之间,通过数据(datain)、地址线(addrin)、控制(reset, write_e)和信号线(clk)等与MPU建立联系。

图3 外部RAM IP组件的结构

在这个设计中对外部数据存储器IP组件ram_fct的要求是:ram_fct接受来自MPU的指令,如复位、读/写等。ram_fct按照指令的要求产生一系列控制信号和相应的时序来控制外部数据存储器,完成相应的操作。实际上,ram_fct对外部数据存储器的操控主要包括外部数据存储器的片选、读写控制、传送数据和地址、高低字节控制等。

当ram_fct的输入信号 是低电平时,复位电路(Reset Circuit)开始工作,进行初始化操作、对标志和状态清零、设定相关常数等。

时钟调节电路(CLOCk Regulator)主要为定时器提供具有高质量波形的时钟。为满足运行中不同时序的需要。

从MPU来的地址(addrin)和控制(write_e)信息被送到译码器(Decoder)。译码器根据不同的地址和控制信息产生相应的指令标志,如读写、选择等。并把指令标志送给控制电路(Control Circuit)。

控制电路(Control Circuit)是ram_fct的核心。它控制数据输入寄存器(Data_in Register)、数据输出寄存器(Data_out Register)、控制寄存器(Control Register)和数据总线三态门(Bus-tri)。控制电路根据指令标志和时序来操作不同的寄存器,实现ram_fct的管理和运行。

数据输入寄存器接受来自MPU的数据,并根据需要通过三态门送数据到数据输出寄存器或外部数据存储器数据线ram_data[5]。在写数据时,数据直接由三态门输出到外部数据存储器;读数据时,数据从ram_dat读入,从数据输出寄存器把数据通过数据线dataout送到MPU数据总线上。

控制寄存器产生操作外部数据存储器的控制信号,如外部数据存储器片选信号(ram_cs)、读写控制信号(ram_we)、输出允许信号(ram_oe)、低字节选择信号(ram_lb)、高字节选择信号(ram_ub)等。

实际上ram_fct的运行操作主要是对各种控制、状态和数据信号进行管理[6]。

该 IP组件 的VHDL程序结构如下:

仿真测试的结果显示,这个设计是可行的。由于外部数据存储器IP组件可以直接控制外部数据存储器的数据操作,大大简化了MPU操作外部数据存储器的程序,从而提高了运行效率、加快了数据操作的速度。

4 结论

移动操作 SoC 是深具市场潜力的嵌入式系统分支,其外部接口IP组件的设计对于移动操作SoC的推广使用具有重要意义。通过对外部数据存储器IP组件ram_fct的设计和仿真,说明基于PLD的IP组件可以用来控制完成对外部数据存储器的操作,还能大大提高系统的运行效率。

本文作者创新点在于把移动操作SoC和IP组件设计联系起来,并通过一个具体例子介绍了如何设计移动操作SoC的外部接口IP组件。

参考文献

1.王越. 嵌入式系统的系统性讨论[C]. 第三届全国高校嵌入式系统教学研讨会报告集,2005; 1-5.

2.S. Heath, Embedded SystEMS Design [M],second edition, New York: Newnes, 2003.

3. Bill Yuan, ALTEra New DevICes Introduction [C], Notes on 2004 Altera China University Professors’ Conference, Shanghai, China, Oct. 2004, 2-23.

4. O.H. James and D.F. Michael. Rapid PrototyPINg of Digital Systems[M], 2nd edn. Boston: Kluwer, 2003.

5.王彦瑜,郭玉辉,乔卫民. 并行设备总线嵌入式控制系统设计[J]. 微计算机信息, 2006;(2-2):56-57.

6.LIU Limin. A Prototyping IP Hardware for SOPC with Single Instruction Driving[C]. 2006 International Conference on Communications, Circuits and Systems Proceedings, IEEE Press, 2006, 559-562.

本文关键字:接口 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术