����1.����

���������ֳ�ʽ����ͨѶϵͳ�ȵķ�չ����ѹ ���� ����������·������Խ��Խ�࣬��˵��� ������ ��Ԫ��������Ѿ������������ ALU ������������Ҫ����ɲ��֣����� ȫ���� ��·�����������·�Ļ�����Ԫ����Ƶ��Ŀ��ټӷ�����Ԫ�ǻ�õ��ĸ��������·�Ĺؼ���ALU��Ԫ����Ʊ��Ƕ��ֶ����ģ������������Ȼ��һ����Ҫ�Ĺ�ע�㣬��Ϊ�������Ӱ���˹��ܵ�ԪALU����Ƹ����ԡ�����������Ҫ��ȴ���ì�ܵ������ǹ��ĺ��ٶȡ��빦�Ľ�����ص�һ�������ǵ�·�ܹ�������͵�ѹ, ����һ���Ǿ���ܵ���������ȫ��������ܵ������ּ����Ӱ����ALU��Ԫ�ľ�������������ȫ���������Ҳ��ALU����б����ص㿼�ǵ�һ���֡��������е�ȫ��������ư����������֡�1-8���о�̬CMOS��·����̬��·�����ܺʹ�������������ȫ��̬CMOS��·���ͳ�ģ�����Ҫ28�����ӡ���̬��·�ܼ���ļ��پ���ܵ��������Ƕ�·����ȴ�ܴ�ʹ�ô���������һ����ѡ�Ľ��͵�·�����Եķ������ڡ�1���л��ڴ����źͷ�������ȫ��������и�ʹ����20��16������ܣ�Ϊ�˵õ����ٹ��ӵ�ȫ�������ڡ�2���л���XOR/XNOR�Ĵ���������·��ɵ�ȫ����ֻ����14�����ӣ��ڡ�3���У�������һ�����ڴ���ܵľ�̬�����ָ�ȫ������SERE������ֻʹ����10�����ӣ��Ҳ������ԳƵĹ���С�����������ͬ�����������ٶȱȽ�����ͬʱ�����Ʋ���������������Ϊ�ڵ͵�ѹ�¹���ʱ�ж෧ֵ��ʧ���⡣�ڡ�4����һ���µĻ���ѡ���·��10��ȫ������Ʊ������Ȼ��������Ҳͬ���ж෧ֵ��ʧ���⣬�����ڲ����ڵ͵�ѹ����ģʽ����ȷ�Ĺ�����ǰ���ᵽ��10��ȫ�������ǻ���ͼ1��ԭ�����ġ����е�ALU��Ԫ������һ���µ�10��ȫ�����������Լ��ֵᷧ��ʧ���⣬�����ƿ�����ʹ���������ӵ��������ɿ��ٵIJ��мӷ�����RCA��ͬʱ���ֽϵ͵�������ģ����⣬�����ƿ����ڽϵ͵Ĺ�����ѹ����ȷ���С�

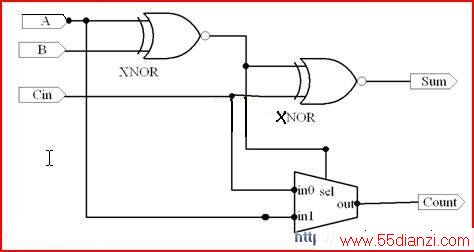

ͼ1 .���е�10��ȫ�����ṹ

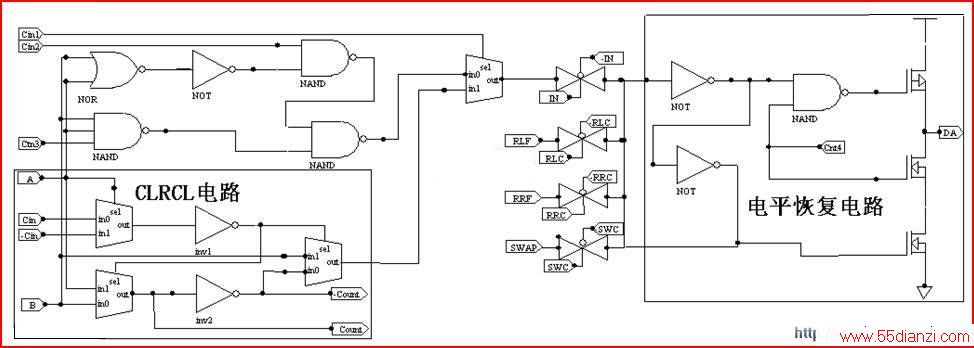

����2.�µĻ���CLRCLȫ������ALU��Ԫ

�������ȿ���ȫ��������ƣ�ȫ������������ʽΪ��

Sum=(A��B)��Cin+(A��B) ��!Cin Count=(A��B) ��Cin+(A��B) ��A

�������Կ���������������ģ����Ҫʹ�èD�DXOR��2ѡ1ѡ������һ��XOR/XNOR�����ô�������ֻ���ĸ����ӾͿ��Դﵽ��5����һ��2ѡ1ѡ������������������ʵ�֡�������Щ��·���в�ͬ�̶ȵķ�ֵ��ѹ��ʧ��������ʹ��ʱ����С�ģ����н�����һ���µ�ȫ�ӵ�·�����ȫ�������ص��ǽ�λ����ƽ�ָ���֮Ϊ��Complementary and Level Restoring Carry LogIC or CLRCL����Ŀ����Ϊ�˼�С��·�ĸ����Ժʹﵽ���ٵļ���������Ϊ�˱����λ���Ķ෧ֵ��ѹ��ʧ��Ϊ����дȫ�����ĺ��Լ���λ����ʽ��

Sum =(A��Cin) ��!Cout+(A��Cin) ��B Count =(A��Cin) ��B+(A��Cin) ��A

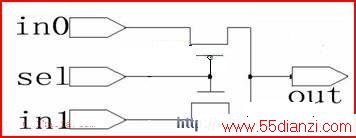

�����Ľ���ĵ�·ͼ��ͼ2.����MUX�ĵ�·��ͼ3��ʾ��������Ƶĺ���֮���������¼��㣺���ȣ�������ʹ���з�ֵ��ʧ���ź���Ϊ��һ����Ԫ�Ŀ����źţ����������е�10��ȫ�������ձ���ڵ����⣬�⽫�����ڵ�·������ʱ���ж෧ֵ��ѹ��ʧ�Ӷ�ʹ��·������ȷ�������ڶ����ڴ�������ȥ����û�л���Ľ�λ�źŴ��͡�����Elmore��ʽ�������ӳ�ʱ��������Ĵ�������Ŀ�Ƕ��η��Ĺ�ϵ��6������ʹ���е���Ŀ�ļ������ȣ��������ӳ�Ҳ�Dz������ܵġ�

�����ԭͼ

ͼ2.�µ�1λALU��Ԫ��·ͼ

ͼ3 .MUX ��MOS��·ͼ

��������ͼ2��ȫ�������ֵ�·��ʾ��XNOR��·������һ��2ѡ1ѡ������һ����������ʵ�֣�����������Ĺ�������������һ��������INV1��������������������������ѹ����ʧ������������������������2ѡ1ѡ����һ��ʵ�ֺ��Լ���λ���ܣ��������Լ���λ�źŵķ�ֵ��ѹ��ʧ���Կ�����һ��|V t|���ڶ���������INV2�ڽ�λ���г䵱��һ�������������ã��Ӷ������˽�λ�Ĵ��ͣ�������ͬʱ����������ṩ��һ����λ�Ļ����źţ���Count������һ����·ʹ�á�����ȫ����ȫ�������ֵ�·��ֻ��Ҫ10�����ӣ�5��PMOS��5��NMOS��������Ŀǰ������֪�����ٵ�ʵ��ȫ������·�ľ������Ŀ��

�����������ơ����ƺ�SWAP���ܿ���ͨ����������ʵ�֣���Figure 2�Ҳ��֣���ͨ����ͬ�Ŀ����źſ�������ʵ����Щ���ܡ�

����ǰ���ᵽ�˱���������ĵ�·����������ֵ��ѹ����ʧ��Ϊ�˺�����·����ȷ�������ǿ��Լ�һ����ƽ�ָ���·��ͬʱ�����·�����Լӿ��·�Ĵ����ٶȣ���Figure 2�Ұ벿�֣�,�ڴ˻ָ���·������ʹ����һ�������źţ�Cnt4����ʵ����̬�ŵĹ����Կ����źŵ����������ⲿ�ֵ�·������źŻ�ȡ���������ദ�������źŲ��õ��Dz�����ʽ������Ϊ�����ʵ���ṩ�˱�����

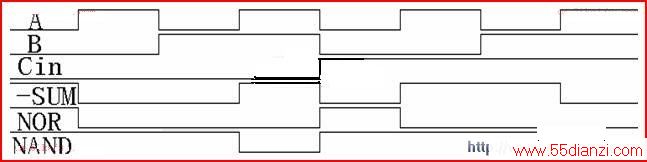

����3. ��·�����ͷ�����

����һЩ������ȫ������ƽ������ͱ��ĵ�ȫ�����Ƚϣ���Ϊ��Ƶ�Ŀ���ǽ��͵�·�ĸ����Ժ���ߵ�·���ٶ��Լ�������ĵĽ��ͣ�������Ҫ��ע�������ٲ����ڴ����ŵ�ȫ����֮��ıȽϡ����е�ȫ�����ܽ����±�2��

������0.35um�����·���һЩ10�ܵ�ȫ������DC���ԣ�����VddΪ3.3v���������ģ�W/L��p=1.4um/0.35um �Լ�(W/L)n=0.7um/0.35um��table3�������⣬�˵�·��1.9v�ĵ�ѹ����Ȼ������ȷ��������Ϊ��һ���� ���� �ṩ��һ���ܺõ�;����

������������·����DC�������õ�������·�Ĺ���Ϊ12.12 uw����ʱ1.5ns,��������ͼ5��������AC����,�����·�Ĺ���Ƶ��Ҳ�DZȽϸߵġ�

�����ԭͼ

ͼ5 . ��·������

����4������

�������������һ���µ�1λ�� ALU ��Ԫ���������ALU��Ԫ��DC���棬�����ںܵ͵Ĺ�����ѹ�¹���������С���ٶȿ죻��AC���棬���ڲ�����CLRCLȫ�������Թ����ںܸߵ�Ƶ���¡�ͬʱ���Ƚ������е�һЩȫ���������ܣ����Կ������е�CLRCL��·����ʹ�õľ���ܵ���Ŀ���٣�ͬʱ���Ĺ��ĺ��ٶ�����Ҳ�DZȽ�������,����������1λALU�����ܡ�

�������Ĵ������µ㣺

�����������Ŀǰ��RISC�ṹ��MCU/MPU������Ҫʹ�õ��ģ�С��������ٵ�ALU��Ԫ�������һ���µĽṹ��ALU��Ԫ�ṹ���ڴ˽ṹ��ʹ�õ�ȫ������Ŀǰ�Ƚ����е�10��Tȫ������ͨ����ȫ���������������飬ʹ����ȫ�����ڼ����ṹ�в�������෧ֵ��ʧ�����������ڵ�·������ֲ����˵�ƽ�ָ��ṹ��ʹ��·��������κܺã�ͬʱ���ֽṹ�����еĽṹ����������Ե�������ٶȣ����ķ�������ơ�

�����ο����ף�

����[1] N.Zhuang and H. Wu,��A new design of the COMS full adder,�� IEEE J. of solid state circuits, Vlo.27,pp.840-844,May 1992.

���Ĺؼ��֣�������ϵ��ʽDSP/FPGA��������Ƭ��-�����豸 - DSP/FPGA����