伴随着Internet的迅速发展,IP已经成为综合业务通信的首选协议,其承载的信息量也在成倍增长,如何利用现有的电信资源组建宽带IP网络是近年来研究的热点。目前,比较成熟的技术主要有IP over SDH(POS)和IP over ATM(POA)。POS将IP包直接装入SDH的虚容器中,通道开销少、实现简单,具有自动保护切换功能;POA的复接过程比较复杂,可以通过高系统开销提供较好的服务质量保证(QOS)。从目前的市场看,各大通信设备商都推出了基于POS/POA的产品,但总体成本较高,主要面向的是一些高端应用。对于带宽需求在十几兆以下的点对点通信而言,上述两种技术的优势并不明显。本文介绍的 适配电路 将 以太网 数据适配到E1信道传输,通过配置E1信道数量控制带宽,针对这类应用提供了一种经济灵活的解决方案。

适配电路的一侧为MII标准以太网MAC接口,采用100MHz/全双工模式,另一侧是8路E1(HDB3)差分接口。发送方向将以太网数据封装为HDLC帧,反向复用到1~8路可配E1信道传输,接收方向同步多路E1,还原出以太网数据。带宽从2MHz到16MHz(1~8路E1)可配,接收侧多路E1之间可以容纳16毫秒的延时。

鉴于目前国内类似产品较少,而ASIC开发成本较高,本电路采用VHDL编程→ FPGA 实现设计流程。

1反向复用定义

反向复用的基本概念就是把一路高速数据适配到多路低速信道中传输,提供相当于多路低速之和的传输带宽。对于点对点通信,主要关心以下几点性能。

1.1 带宽利用率

低速信道在传输高速数据的同时,必然有附加的开销,会影响带宽利用率。在本设计中,以太网包进入适配电路后封装成HDLC帧需要四字节的附加信息。E1帧在传输HDLC数据的同时要携带的同步信息,占用6.25%带宽。综合上述两点,有效数据平均带宽利用率大约在90%。

1.2 容纳延时

由于各路低速信道在传输过程中经历的路径不同,到达对端后各路间会有延时,设计中要考虑如何消除这部分延时。

1.3 线路故障处理

算法设计中必需有同步保护状态机,保证传输信道出现错误时,算法不会产生过高的附加误码率,并且在信道错误恢复时,保证数据传输同步恢复。

1.4 数据包突发性

以太网的满发送速率为100MHz,而低速信道的最大可配带宽为16MHz,这将导致即使平均流量小于配置带宽,一个短时间内,接收的数据量还有可能远大于传输带宽。所以在以太网数据的输入侧必须设计高容量的缓存队列以容纳一定的突发数据包。

2 算法设计

以下就设计中一些核心电路的算法做具体说明。

2.1 以太网数据→多路E1反向复用

数据反向适配一般可以采用三种方式:包间插、比特间插和字节间插。所谓包间插就是指数据包到达后,连续检测各个E1信道,在第一个查到的空闲信道上顺序传输整个数据包,下一包到达后再重复这一过程。这种方式的优点是设计简单,在对端也不需要对多路E1进行同步,各路数据可单独处理。缺点是由于各路E1传输过程中经历延时不同,导致对端接收数据包的顺序与发端顺序有较大差别。考虑到发包比较稀疏的情况,一个长包完全可以在一路E1中传递,而其它E1通道没有数据包传送。这样,一方面造成带宽浪费,另一方面也引入较大的转发延时。

比特间插在传输过程中没有包的概念,只是顺序从以太网数据输入缓存区内读出比特流并按1→n(n路E1)循环编号,编号为i的比特在第i路E1中传输。这种设计电路十分复杂,对端要对多路E1同步到比特单位才能还原出有效数据。其优点就是没有带宽的浪费和输入输出包顺序的变化,转发延时也是固定的。

本设计采用的字节间插是比较折中的解决方案。它的基本原理与比特间插类似,但从缓存区读出的数据和编号都是以字节为单位,每个字节经过串并转后在对应编号的E1信道中传输。它继承了比特间插的优点,同时由于对端只需同步到字节单位上,处理时钟较为宽裕,同步电路设计也就相对简单。其具体的算法实现如下:

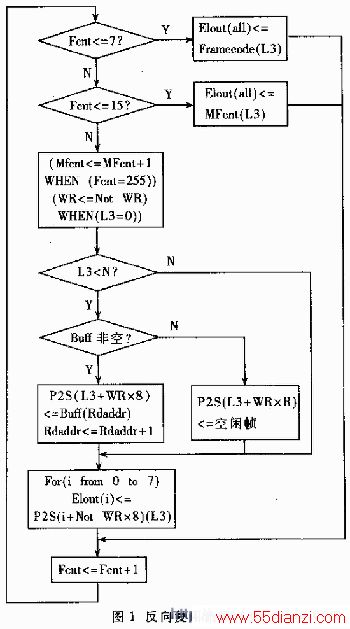

以太网数据包进入适配电路后封装成HDLC帧存入缓存区Buff,Buff的出口侧速率与多路E1信道传输速率匹配,一个2MHz时钟周期内完成的操作如图1所示。

图中,

Fcnt:8比特帧计数(E1帧有256个bit);

MFcnt:8比特复帧计数;

L3:Fcnt的低三位比特;

E1out:输出8路E1数据(8bit);

Framecode:E1帧同步码“10011011”;

N:配置E1路数(1~8);

Rdaddr:Buff读地址;

P2S:2×8字节并串转换存储区,写一组8字节时,读另一组8字节;

WR:P2S读写区域指示(0,1)。

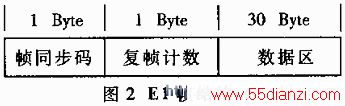

输出的E1帧格式如图2所示,帧同步码和复帧计数都是为接收端提供同步信息。

2.2 E1接收数据同步

E1接收侧要完成的功能是从多路E1数据中还原出 以太网 数据包。简单看就是发送侧反向复用的逆过程,通过高速时钟循环从1→n路E1中各读出一字节合成一路数据。但由于各路E1在传递过程中经过延时不同,同一时刻到达字节不对齐,在合并前必须对多路E1进行同步。考虑到同步过程的复杂性,在设计算法时采用了分步处理,以降低复杂度。

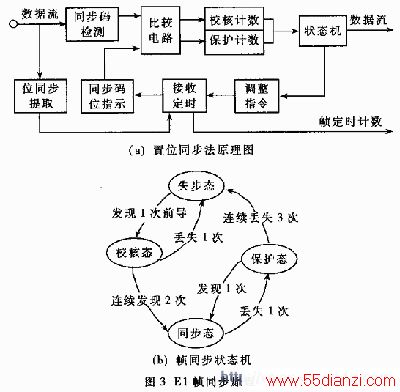

第一步处理是根据帧结构中帧同步码,通过置位同步法完成单路E1帧同步,同步原理图和状态机如图3所示。同步后每路输出数据产生独立的帧定时计数器TM,从0→31标记E1帧对应的32(256bit)字节,其中第0字节即帧同步码Framecode,第一字节即复帧计数器MFcnt。这一步并未涉及多路间的延时消除。

根据状态转移图确定的状态参数,α(搜索保护帧数)=3、β(同步保护帧数)=4。设线中误码率Pe=10-3,L(帧同步码长度)=8,Ts(E1帧周期)=125μs,得出同步机的性能指标:

平均同步时间≈[1/(L×Pe)β-(α-1/2)] ×Ts≈8.5小时

同步失帧误码率≈1/2(α-1/2)(L×Pe)β≈5×10 -9

可见在较高的误码率下(10 -3),同步机还是能够保证比较好的同步质量,平绝每8.5小时出现一次失步,引入的附加误码率也只有10 -9量级。

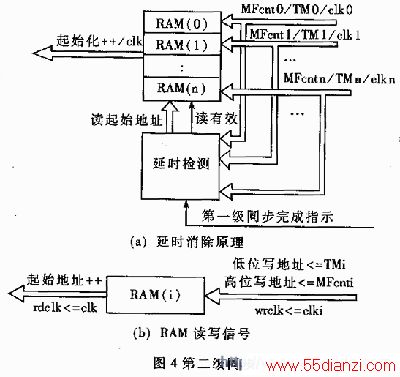

第二步处理根据E1帧同步产生的帧计数和每感数据中的复帧计数消除各之间的延时及时钟相位差。其基本原理见图4。在第0路数据延时最小的情况下,设第一步完成同步后到达RAM(0)的数据为第M复帧第T字节,数据以各自计数为写地址存入RAM,延时检测通过计数不停检测,直到所有路第M复帧T字节到达后,再统一以clk为读时钟,以M&T为起始地址顺序从RAM中读出数据。由于MFcnt最大为255,第二步同步能容纳的线路时延在(-128,+128)帧之间,超过这个范围MFcnt所代表的时延就可能是(n(任意整数) ×128+MFcnt)帧,所以该算法能承受的最大线路延时为:

128×Ts(帧周期)=16ms

在线路误码率较低时,E1帧同步丢失较少,帧定时计数TM可以确定,影响第二步处理的只有数据中的复帧计数字节。在没有保护的条件下,假设目前某一路MFcnt由于误码使其读数由正确值A变为B,因为下一轮开始时A、B位置帧会重写,不会对数据整体逻辑产生较大影响,其它位置的误码会在后续的HDLC帧同步处理中检测。如果线睡误码率较高,由于E1会频繁失步使第二步处理根本无法进行。出于述考虑该步算法设计没有采用状态机保护。

2.3 HDB3时钟提取

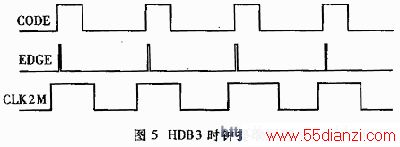

从接收的E1信号HDB3编码中提取时钟的原理如图5所示。首先通过一个高速时钟采样HDB3的码流(CODE)得到数据变化沿(EDGE),再根据EDGE位置由高速时钟分频出对应的2MHz时钟。

3 电路设计

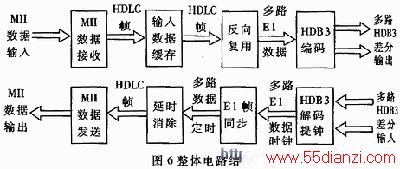

整体电路结构如图6所示。在输入数据缓存和消延时两部分处理中,由于需要较大存储空间,采用两块外挂的SSRAM。内部处理以字节为单位,全同步电路设计,对应以太网侧处理速率为12.5MHz,对尖E1侧时钟为256kHz(2.048MHz/8)。两侧速率匹配通过高速时钟采样低速时钟完成。

4 时序分析

从逻辑验证到 FPGA 实现主要区别是增加了实现布线、引脚间的时延。使系统失效的时序问题主要有以下几点:

本文关键字:以太网 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术