为了持续提升性能而又不至于因过热导致故障,微 处理器 正朝向 多核 心方向发展。但主流 软件 至今却尚未能找到使用这种新 并行 机制的途径。

专用编程方法已开始在一些应用中受到青睐。然而,软件产业可能还需要十年或更长的时间,才能以一种较有组织的形式赶上多核心硬件的发展;在此同时,这条道路上还存在着一些难以跨越的障碍。

“所有攸关性能的关键程序都必须重新编写,”斯坦福大学PervasiveParallelismLab总监KunleOlukotun说。该团队是致力于解决这个被当今计算机科学视为最棘手问题的众多研究小组之一。

“最后不是被迫重新编写这些程序代码,就是只好将它淘汰,”Olukotun说。他在最近举行的‘多核心虚拟会议’(MultICoreVirtualConference)上针对该主题发表专题演讲。

“这是电信公司目前所面临的最大问题之一,”近期将出版一本有关电信设计专书的系统架构师AlexBachmutsky表示,“它们的应用程序并不是针对多核心和执行绪编写的,而且这些程序规模庞大,包含了数百万或数千万行的程序代码。”

无所不在的C语言“是最糟糕的工具,因为它在本质上是连续性的语言,这使得算法中原有的并行机制变得模糊不清,”DSP咨询公司BerkeleyDesignTechnology总裁JeffBier说。

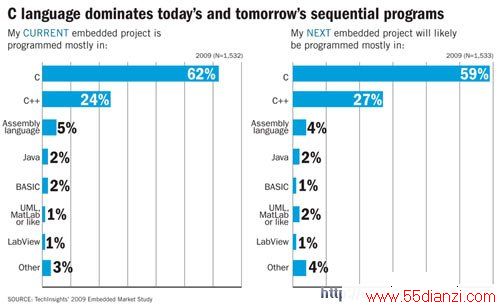

根据TechInsights公司在今年初所进行的一项研究,在接受访谈的嵌入式系统开发人员中,约有62%表示最近的计画是以C语言写的;还有24%表示使用了C++。

研究者们已经开发出许多并行编程语言,但没有哪一种是万能的,而且要成为被市场接纳的商品都还有很长的路要走。Olukotun预测最终将出现一系列自动寻找并行机制的高阶专用工具。

多核心处理器也正致力于投入主流设计领域,系统、芯片与工具开发商们也正提出一系列确实可用的开发工具。

其中一部份是现有的多核心处理工具,例如目前用于芯片级编程的OpenMP。英特尔(Intel)及其它公司们已经发布了用来管理软件执行绪的工具库。CilkArts公司等新兴公司也在传统的程序代码中植入关键词来协助寻找并行机制。

“各种方法都互有利弊,”飞思卡尔半导体(Freescale)软件研发总监RobOshana指出。

开发人员将需要新的建模工具来解决如何在早期设计阶段划分应用的问题,Oshana表示。另外,并行除错器已初露曙光,在一个复杂的系统单芯片中,只要能让通过多个核心、加速器和互连的资料达到可视化,将可望协助设计人最佳化其程序代码。

短时间来看,许多芯片制造商正试图将最多的并行程序代码加载于软件堆栈中。但在某些情况下,他们有时候会因为过度开发,反而无法提供一些较通用的并行应用程序,飞思卡尔公司资深系统架构师SteveCole表示。

“它应该能够包含我们的应用程序与第三方应用程序,以及操作系统和工具,”Cole说,“这才是业界该走的方向。”

为了开发这样的产品,飞思卡尔已经将其多核心软件团队人数增加了一倍之多,Cole说。

同时, OEM 们也正在寻找自己的方法来解决这些问题。电信架构师Bachmutsky指出,控制台设计正采用系统级对称多处理(SMP)工具来管理基于SMP操作系统的多核心芯片。而其设计结果“看起来就像是具有多线卡与负载均衡器,可在各刀锋背板间分配流量的系统,”他说。

由于资料面设计通常使用汇编语言编码,因此,要把性能提高10倍以上的难度更大。这意味着它无法负担SMP结构的共享内存开销。

开发人员们必须仔细地划分任务并分配给各个核心,观察数据间的依赖性。他们必须制订在不同任务间传递的详细讯息方案,并找出在数据和控制台软件堆栈间的通讯方式,Bachmutsky说。

采用汇编程序码,“你就与硅晶制造商及工具库密切相连,你无法轻易地把软件移植到另一个处理器,”他说。“但无论你选择哪一种方案,都意味着将与该方案密切相关。”

图1:C语言主导当今与明日的循序程序设计。

先进技术进展

一些特殊应用在 并行 处理的道路上取得了更多进展,但所使用的仍是专有的芯片与工具。例如,针对石油与天然气勘探等一连串应用中,Nvidia采用其具有Cuda环境的绘图芯片展开了大量并行编程工作。

一些设计公司表示已成功实现了并行处理的先进技术。例如,英国CambridgeConsultants公司使用了PICoChip公司在单芯片内封装250个核心的组件,完成了3G和WiMax基地台的合约设计工作。

对于这些应用而言,CambridgeConsultants公司发现PicoChip的组件实际上比4核心的数字讯号 处理器 (DSP)更好用。“这一开始似乎令人百思不解,但与传统的单核心或核心数较少的DSP相较,使用PicoChip的组件所开发出的程序更简短、可靠且产出品质更高,”在CambridgeConsultants主导DSP研发团队的MontyBarlow解释。

“内含众 多核 心的多核心架构可以把功能划分到各颗核心中,在系统已知各部份不会产生负面影响前提下,可分别开发并测试这些功能,而后再转入系统的其它部份,”Barlow指出,“另一种替代方案是依执行绪编写程序,并取决于操作系统的运作情形来分配时间,但这些任务是以一种无关联的速率执行,某一天,许多任务可能会团结起来与你作对,而某些任务还可能会延迟而导致失败。”

采用新方法就必须为PicoChip的组件重新编写 软件 。但Barlow说,他认为值得在架构方面进行更多工作,以便使后续开发过程更顺利。

分析师JeffBier指出,PicoChip和Tilera等开发大规模多核心系统的新兴公司们使用了完全不同的软件工具,这使得从他们的架构中移植软件的难度极大,风险更高。“这种创新很有意义但难度极大,因为这些新兴公司必须在芯片和并行软件方面取得成功,”他说。

“我预计这些特殊的架构存在时间不会太长,”史丹佛大学的Olukotun说。“随着越来越多通用环境的性能更强且功效更高,这些特殊架构很快会被取代。”

Olukotun相信,实验室的研究成果最终将为软件堆栈带来创新。他们将实现并行程序代码自动化产生,开发人员将无需再与执行绪、讯息传送、内存同步存取和其它结构打交道。

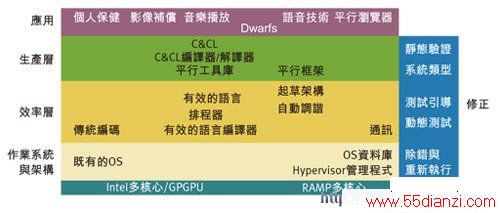

该实验室的开发人员们将以高阶特定领域语言(DSL)进行编程,使其可为一系列具有先进排程器的执行时间(runtime)环境自动产生并行任务。这些执行时间系统将“结合不同组件以开发出不同的执行模式,以便产生串流、原子、容错、安全或执行监控作业,”Olukotun说。

飞思卡尔的Oshana也认同这一观点。“许多应用均乐于接受更多抽象观念,以实现更好的整合,”他说。例如,可执行多操作系统的hypervisor虚拟管理程序将变得越来越普及。

“这些新的想法能否被接纳?它将取决于开发人员感受在编程多核心处理器时的痛苦指数,”Olukotun说。

但在很长一段时间内,这种痛苦可能还不至于普遍存在。在TechInsights公司的调查中,只有大约7%的嵌入式开发人员表示正在使用多核心处理器,而这个数字已高于两年前的4%了。

LinleyGroup公司首席分析师LinleyGwennap今年三月时曾表示,由于并行编程的复杂性,到2012年,具有4颗或更多核心的处理器在通讯系统市场上的比例很可能只略多于10%。Gwennap并预测,2012年以前,双核心设计的市占率将达到20%。

图2:柏克莱大学的研究人员指出,未来的并行应用程序发展模式将从软件堆栈的每一层开始进行改变。