高分辨率全帧CCD芯片FTF4027M的驱动电路设计

高分辨率全帧CCD芯片FTF4027M的驱动电路设计

点击数:7802 次 录入时间:03-04 11:38:45 整理:http://www.55dianzi.com DSP/FPGA技术

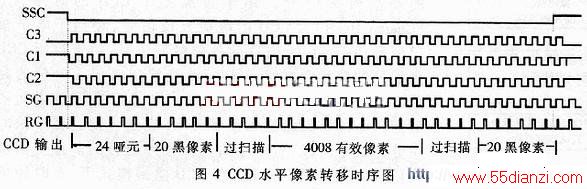

3.2.3水平像素转移的 驱动 时序 该时序涉及C1、C2、C3、RG、SG,其频率都为25MHz。SSC下降沿到来时标志着一次垂直行转移的结束和一次水平像素转移的开始,转移原理和行转移原理一样,三相C时钟信号要严格满足三相交迭原理,占空比为3:6,也就是高低电平保持时间一样。在电荷由光敏区向输出寄存器转移的过程中(见图4),在SSC下降沿到来之前,C3应该保持低电平,使像素在输出寄存器的隔离开来,而C1和C2应该保持高电平,使转移下隔断的电荷在这两个电极之下积聚起来,为下一步的水平转移输出作准备。

点击看原图

4 实验与讨论

系统设计完成后,根据 CCD 的时序村注,经仿真调试可以产生出相应的驱动脉冲和偏置电压。但是由于系统的后续图像处理和传输部分还没有设计好,所以无法进行图像采集。该驱动电路的研制结果表明,采用现在芯片进行系统设计有它自身的好处,可以简化设计,而且调试简单、可扩展性也比较强。

上一页 [1] [2]

本文关键字:分辨率 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术