概述

近二十年来,全球半导体产业的飞速发展带动相关的软件、硬件设计达到新的水平,使得很多比较复杂的数字信号处理算法可以 实时 实现并且得到广泛应用。突出的代表就是数字信号处理器( DSP )与语音信号压缩编码算法相结合,并且在日常通信系统中得到广泛应用,例如数字移动电话、IP电话等。随着网络通信的发展、微处理器和信号处理专用芯片的发展,也为语音处理技术的应用提供了更加广阔的平台。所有这些因素都促进了对更加有效、可靠、高质量的 语音编码 系统的需要,从而促进了语音编码技术的持续发展。在最近一些年内,语音压缩编码技术有了很大的发展。最早的标准化语音编码标准是70年代CCITT公布的G.711 64kb/s脉冲编码调制PCM。此后ITU又先后公布了G.721 32kb/s自适应差分编码(ADPCM)、G.728 16kb/s短延时码本激励线性预测编码(LD-CELP)。此外还有一些政府和组织制定的语音标准,例如用于西欧数字移动通信的13kb/s具有长时预 测规则码激励(RPE-LPT)的线性预测方案,北美数字移动通信标准8kb/s矢量和激励线性预测(VSELP)方案等。1999年欧洲通信标准协会(ETSI)推出了基于码激励线性预测编码(CELP)的第三代移动通信语音编码标准自适应多速率语音编码器(AMR),其中最低速率为4.75kb/s,达到通信质量。1995年ITU公布G.723.1,编码算法有两种,5.3kb/s的ACELP和6.3kb/s的MP-MLQ算法,主要用于IP电话。1996年ITU公布了G.728 8kb/s的CS-ACELP算法,可以用于IP电话、卫星通信、语音存储等多个领域。目前,ITU正在致力于制定4kb/s的语音编码国际标准,该算法将达到长途质量。针对一些特殊应用,如保密通信、军用通信、应急通信等,许多国际组织、国家也研制了各种不同速率的语音压缩编码速率,例如美国政府为保密通信用开发的2.4和1.2kb/s MELP算法。我国近几年也研制了0.6、1.2、2.4kb/s及其它速率语音压缩编码算法,达到并且超过了国外同速率编码的质量。

DSP在近20年内一直在高速发展,运算能力不断提高,片上资源和接口更加丰富,而单位运算所需功耗不断降低。下面给出几个主要厂家的DSP产品。

TI的DSP主要有四大系列:

C5000系列(定点,低功耗):适合个人与便携上网及无线通信应用。80-400MIPS。

C2000系列(定点,控制器):针对控制进行优化的DSP。

C6000系列(高性能):适合宽带网络和数字影像应用。

OMAP系列(双核芯片):适合低功耗移动设备和多媒体PDA。

ADI的DSP主要有四大系列:

21xx系列:16定点DSP,内部REM大,外围接口多,适合作为控制类芯片使用。

SHARC系列:32位浮点DSP,21160 21161提供与大内存容量结合的简单浮点算法,具有高水平的浮点性能。

TigerSHARC系列:比SHARC具有更高的浮点运算功能TS101,TS201

Blackfin系列:高性能16位DSP信号处理与通用微控制器易使用的性能结合。

Motolora的DSP:

DSP56800,16BIT定点DSP,通用型DSP。

DSP563XX,24bit定点DSP, 通用型DSP。

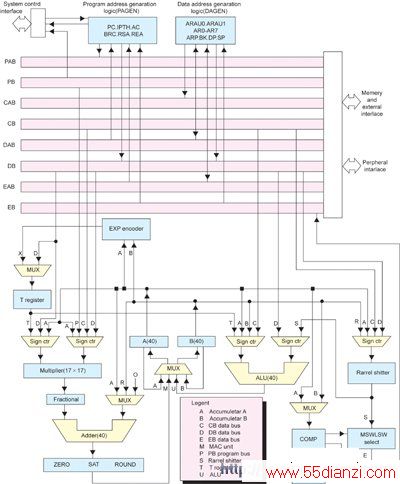

图1 C54xDSP结构框图

TMS320 C54x系列DSP芯片简介及硬件设计

TMS320 C54x系列DSP芯片是使用静态CMOS技术制造的。其方框图见图1,从图中可以看出C54x系列DSP芯片具有以下功能单元:

总线

C54x共有八条总线分别是:

PB: 程序读取总线

CB: 数据读取总线1

DB: 数据读取总线2

EB: 数据写入总线

PAB: 程序读取地址总线

CAB: 数据读取地址总线1

DAB: 数据读取地址总线2

EAB: 数据写入地址总线

中央处理器(CPU)

CPU由以下几个部件组成:

先进的多总线结构: 包括三个独立的数据总线和一个程序总线

40位的算术逻辑单元: 包括一个40位移位器和两个独立的40位累加器

17bit 17bit的并行乘法器同一个专用的加法器相配合: 用来执行不经流水线的单周期乘加(MAC)运算

指数译码器: 可以在一个周期里计算出一个40位累加器的指数值

两个地址生成器: 包括8个辅助寄存器和两个辅助寄存器算术单元

程序控制器: 对指令进行解码、管理流水线和程序流程

片上存储器

C54x共有192K字的寻址能力(64K字的程序区,64K字的数据区,和64K字的I/O区)。

表1给出了部分C54x芯片的片上资源、运算能力、工作电压等。运算能力用MIPS来度量,即每秒能执行一百万条指令的数量。

www.55dianzi.com

片上其它资源

C54x系列中不同产品具有不同的片上外设配置。这些外设有:

软件可编程的等待状态发生器

可编程的库转换

片上锁相环时钟发生器(包括一个内部振荡器或一个外部时钟源)

一个16比特定时器

通用输入输出管脚

同步串行口

异步串行口

C54x系列 DSP 芯片具有以下主要特点:

采用改进哈佛结构,对程序内存和数据内存使用分离的总线。这样可以同时取指令和操作数,提高了运行效率和通用性

先进的CPU设计和为应用设计的硬件逻辑提高了芯片的性能

为快速的后续发展设计的模块化结构

先进的IC处理技术提供了高性能和低功耗

采用5V或3V静态CMOS技术可以进一步降低功耗

Power-down模式可以进一步降低功耗

能源消耗控制: 使用IDLE1,IDLE2,和IDLE3指令进入Power-down模式使用CLKOUT-off控制来禁止CLKOUT信号

高度专门的指令结构提供了快速运算和优化的高阶语言操作

单指令循环和块指令循环功能

本文关键字:语音 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术