C64xx系列DSP有大量的字节可设定的地址空间,程序代码和数据可被存储在统一标准的32位地址空间的任何位置。表l所示的内存映射显示了本板卡采用的DM642处理器的地址空间。在默认状态下,内部的寄存器从0x00000000地址空间开始存储。一部分存储器由软件重新映射为L2高速缓存。DM642的EMIF有4个独立的可设定地址的区域,称为电路使能空间(CEO-3)。本板卡合并形成了64位长的外部存储器端口,将地址空间分割成4个电路使能区,允许对地址空间进行8位、16位、32位和64位的同步或不同步的存取。目前,板卡使用电路使能区CEO,并将其分配给64位的SDRAM总线。CEl-3的电路使能区暂不使用,可以作为今后的扩展,以便分配给8位Flash、UART、FPGA和子板接口等使用。

本板卡在CE0空间连接了64位的SDRAM总线,与2个HY57V283220TP-6相连以构成SDRAM。每个HY57V283220TP-6均为32位数据总线的SDRAM,其中,高 32位存储在1个SDRAM中,低32位存储在另1个SDRAM中,从而满足DM642 64位数据总线的要求。32 MB的SDRAM空间用来存储程序、数据和视频信息。总线由外部PLL驱动设备控制,运行在133 MHz的最佳状态。SDRAM的刷新由DM642自动控制。

DM642可配置EMIF时钟的原始值。本板卡的ECLKIN引脚选用默认值,也可通过分频CPU时钟控制EMIF的时钟频率。在初始化时通过对E-CLKINSEL0和ECLKINSEL1引脚的操作进行设置,它们与EAl9引脚和EA20引脚共同分享EMIF的地址空间。

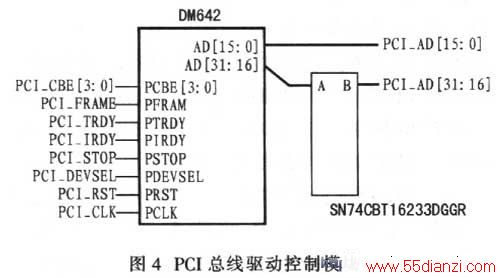

3.4 PCI总线驱动控制模块

PCI总线驱动控制模块由1个SN74CBTl6233型PCI总线桥接电路及其外围电路组成。本模块中的信号按照功能可以分为系统信号、地址数据复用信号和接口控制信号等。系统信号包括CLK和RST,为系统提供时钟和复位。对地址数据复用信号来说,在总线传输操作周期中,1个PCI总线周期由1个地址段和紧随其后的1个或多个数据段组成,其中AD[0-31]是地址数据复用总线,可为PCI接口电路提供地址和数据信号;复用引脚PCBE[0-3]为PCI接口电路提供总线命令信号和字节允许信号。接口控制信号主要由FRAME、TRDY、IRDY和DE-VSEL等信号组成,其中,FRAME信号是总线周期构成信号,由当前总线中主设备驱动,表明1个总线周期的开始和延续;TRDY是目标设备就绪信号,在写操作中,TRDY有效表明从设备已准备好接收数据,而在读操作中,TRDY有效则表明AD[0-31]上已有有效数据;IRDY表明驱动设备已准备好数据;DEVSEL为设备选择信号,当其有效时,说明驱动它的主设备已将其地址译码作为当前操作的目标设备,该信号作为输入信号时,DEVSEL用来表示总线上已有目标设备被选中。其他PCI总线所需但本系统不用的信号则可用高阻态代替。PCI总线驱动控制模块接口电路原理功能框图如图4所示。

本板卡使用DM642型DSP片内集成的1个主/从模式的PCI接口与PCI总线相连,该接口支持PCI 2.2规范,通过PCI总线能够实现DSP与PCI主机的互连。主机可以通过DM642的PCI接口访问整个片内RAM及外部存储器。DSP的EMIF通过EDMA将数据传输到DSP的内存中,EMIF支持同步FIFO,为了能够使PCI总线实时读出视频压缩数据流,并及时地传送给主机,本系统采用了中断机制。当FIFO满时,DSP产生一个中断信号,通知PCI接口模块启动DMA,需传输的数据经FIFO由DSP利用DMA传输方式在计算机和板卡间实现视频压缩码流的高速传输,在提供高速传输接口的同时不影响其他DMA操作。

3.5 电源管理模块

本板卡通过PCI插槽供电,选用AMSl085和AMSl086提供板卡正常工作时的稳压电源。AMSl085、AMSl086均为3端可调节稳压集成电路,AMSl085输出电流为3 A、输出电压为1.5 V/3.3 V.5.O V,AMSl086的输出电流为1.5 A、输出电压为1.5 V/1.8V/3.3 V/5.0 V。它们比较容易使用,而且都有短路电流保护以及过热保护等防护措施,具有高精度的输出电压及工作稳定性。设计时,内部+5 V输入电源被整流为+1.4 V、+1.8 V和+3.3V,其中,+1.4 V电压提供给DSP处理器,+1.8 V电压提供给TVP5150,+3.3 V电压提供给DSP内的I/O和板卡上其他电路。3.3 V和1.4 V电源之间应连接肖特基二极管,保证给DM642内核和外部端口同时供电。

www.55dianzi.com

4 板卡设计的难点及关键技术

本设计方案中.处理器的主频高达720 MHz,SDRAM的最高频率为133 MHz,这对信号完整性及电磁兼容性都是极大的挑战。在 多路视频采集 处理板卡的PCB设计中突出体现以下难点:

一是时序问题,工作频率的提高和信号上升/下降时间的缩短,首先会使设计系统的时序余量缩小甚至出现时序方面的问题。

二是传输线效应导致的信号振荡、过冲和下冲都会对设计系统的故障容限、噪声容限及单调性造成很大的威胁。

三是信号沿的时间下降到l ns后,信号之间的串扰成为很重要的问题。

四是当信号沿的时间接近0.5 ns时,电源系统的稳定性和电磁干扰(EMI)也十分关键。

多路视频采集处理板卡PCB的设计策略如下所述:

(1)高速数字电路设计

为了更快地推出更高性能的产品,电路板设计按6层板考虑,在元器件布局及布线过程中严格遵守高速电路设计原则,为确保系统功能的实现及整机性能指标达到检测标准,在PCB布线时需要特别注意串接电阻降低高速电信号反射的影响及保证同一组数据同步到达。由于信号在顶 层、底层与中间层的传输阻抗和传输速率不一样,因此应尽量将接到同一器件的信号线分布在同一层上,并使导线长度相等。

(2)电源设计

电源是系统正常工作的基础,一般来说,只要电源工作正常,都可以通过JTAG口将程序下载到DM642中,进而调试其他的模块。在设计中,应使用足够多的电源层和地层,对AVDD、DVDD、AGND、DGND分层设计,并将模拟地与数字地单点接地,这样可以避免模拟电路与数字电路相互影响。

5 结束语

笔者在引进和消化 TMS320DM642 的多媒体数字处理技术的基础之上,成功研发了这款多路视频采集处理板卡。本板卡结构紧凑、功能完善、性能可靠、音/视频效果优异、系统升级方便。目前,业内的主流还是基于CIF分辨率的监控记录,今后高分辨率(D1)的监控记录以及采用H.264技术的编码压缩产品的市场需求将逐渐增加,给算法优化及处理器能力的提升提出了新的课题,这将是下一步关注的重点。

本文关键字:硬件 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术