1 引言

视频监控系统是安全防范系统的重要组成部分,也是一种防范能力较强的综合系统。视频监控系统以其直观、方便、信息内容丰富而广泛应用于许多领域。近年来,随着计算机、网络及图像处理、传输技术的飞速发展,视频监控技术也得到长足的进步,集多媒体技术、数字图像处理和远程网络传输等最新技术为一体的多媒体数字监控系统正在逐步取代传统的模拟视频监控系统。目前,市场上专用的视频压缩电路只能实现一种压缩算法,灵活性和可扩展性较差,基本不具备在此基础上进行二次开发的能力;各种基于ISA、PCI等总线的图形采集卡也能在市场上买到,但价格较贵,且处理功能简单,二次开发效率低,不能很好地满足用户的特殊需要。

为了适应多媒体通信技术的发展,美国德州仪器公司推出一款针对视频和图像解决方案的 TMS320DM642 型高性能数字媒体处理器,它是TI公司C6000系列DSP中最新的定点DSP,其核心是C6416型高性能数字信号处理器,具有极强的处理性能、高度的灵活性和可编程性,同时外围集成了非常完整的音频、视频和网络通信等设备及接口,特别适用于机器视觉、医学成像、网络视频监控、数字广播以及基于数字视频/ 图像处理的消费类电子产品等高速DSP应用领域。笔者针对市场客户的需求,设计并实现了一款以TVP5150为视频输入解码器、以PCMl801为音频输入采集电路、以TMS320DM642型DSP为核心处理器的 多路视频采集 兼压缩处理 PCI板卡 ,并将其应用于构建高稳定性、高鲁棒性的多媒体数字监控系统,取得了较好的社会效益和经济效益。

2 TMS320DM642的硬件架构

TMS320DM642采用第二代高性能、先进的超长指令字veLOCiTI.2结构的DSP核及增强的并行机制,在720 MHz的时钟频率下,其处理性能为5 760Ml/s,使得该款DSP成为数字媒体解决方案的首选产品。它不仅拥有高速控制器的操作灵活性,而且具有阵列处理器的数字处理能力。TMS320DM642的外围集成了非常完整的音频、视频和网络通信接口,主要包括:

有关TMS320DM642的详细性能介绍请参照其数据手册。

3 多路视频采集处理板卡硬件设计

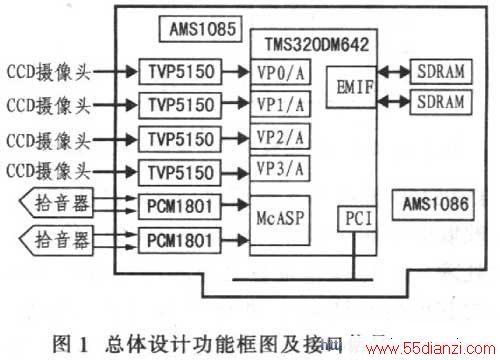

基于TMS320DM642的多路视频采集处理板卡的主要硬件功能模块包括视频输入解码模块、音频输入采集模块、核心DM642型DSP模块、外部存储模块、PCI总线驱动控制模块及电源管理模块等。基本工作原理是由CCD摄像头采集输入的模拟视频信号,经过视频解码器转换成数字视频信号,由拾音器采集输入的模拟音频信号经过音频采集电路转换成数字音频数据,送到DM642,DM642再将采集的音、视频数据用MPEG-4标准编码压缩后通过PCI接口传送到PC上位机,构成数字监控系统。本板卡的总体设计功能框图及接口信号示意图如图1所示,主要由1个TMS320DM642GDK(DSP)、4个TI公司的TVP5150AMl(视频解码器)、2个TI公司的PCMl801U(音频采集电路)、2个Hynix公司的HY57V283220TP-6(SDRAM)、1个SN74CBTl6233DGGR(PCI总线桥接电路)以及AMSl085CM和AMSl086CD(电源管理电路)等组成。

3.1 视频输入解码模块

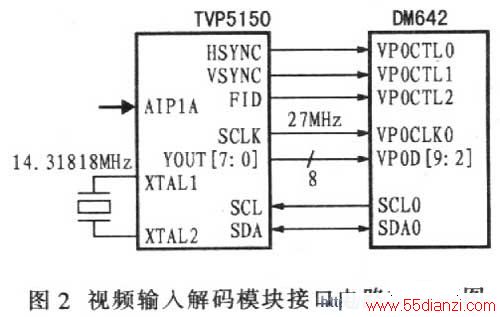

视频输入解码模块由4个TVP5150型视频解码器及外围电路组成,主要功能是将每一路CCD摄像头采集输入的标准PAL制电视模拟信号发送到视频解码器,完成视频图像的箝位及抗混叠滤波等预处理、模拟数字化转换及亮度/色度、水平/垂直同步等信号的分离,实现模拟视频信号转换为数字并行信号BT.656码流格式。TVPSl50可将基带模拟NTSC、PAL及SECAM视频信号转换成数字分量视频信号,正常工作时的功耗仅为115 mW,售价比同系列TI产品更低,并且具有业界最小尺寸的32引脚超薄方型扁平封装(TQFP)。TVPSl50支持2个复合端子或1个S端子输入,可输出ITU-RBT.656,并支持Macrovision复制保护及高级VBI功能。

DM642视频口0、1中的一部分(VPO/A、VPI/A)及视频口2(VP2/A、VP2/B)分别挂接1个TVP5150,视频采集的数据格式为YUV4:2:2,分辨率为CIF(352x288)大小。视频输入解码模块接口电路原理功能框图如图2所示。系统将2个电路的I2C总线接口SCL和SDA分别互连,TVP5150的视频输出口YOUT[0-7]和DM642 VPORT口的VPOD[9-2]相连,TVPSl50的系统时钟SCLK和 DM642VPORT口的VPOCLK0相连。由于采用ITU-R BT.656码流格式,图像的水平同步、垂直同步、场同步等同步信号已内嵌在视频数据流中,并且考虑到DM642每个VPORT口预留的3个用以接收同步信号的VPOCTL[0-2]控制引脚,只能满足一路视频同步信号的要求,所以在设计过程中省略同步信号线的连接。

TVP5l50虽然不支持缩放(Scaling)功能,但是可以截取屏幕的一部分再传输给DM642作后续的压缩处理。具体操作是在对应的寄存器中选择视频流的起始行和结束行,控制图像的纵向长度,选择单行的起始位置和结束位置并利用图像的AVID功能控制图像的水平宽度。

DM642对TVP5l50内部寄存器的访问通过I2C总线实现,在与TVP5l50应答过程中需要从器件TVP5150的地址0x101lIOXl,其中X代表0或者1,并可以在系统上电时配置。TVP5150在上电时会根据YOUT[7]上的电位高低决定X代表O,还是1。这样,TVP5l50作为从器件的地址只有2个:Oxl0111001和0x10111011。DM642要与4个TVP5I50通信,一路I2C总线是不够的,需要通过GPIO接口利用软件模拟I2C总线时序,配置另外两个TVP5150。

采集输出的数字视频数据送入DM642VPORT端口的5 120 Bytes大小的缓冲区。TVP5150在本地时钟的控制下通过EDMA通道自动向DM642 VPORT端口缓冲区单元发送数据,当采集完一场数据时产生DMA中断,并在DMA中断服务程序中根据实际需要完成相应的视频处理,经过实时编码压缩后的视频数据存储到外部SDRAM中。硬件电路需要提供TVP5150所需要的14.31818 MHz时钟频率,DM642可通过I2C总线对TVP5150的参数进行设置。

3.2 音频输入采集模块

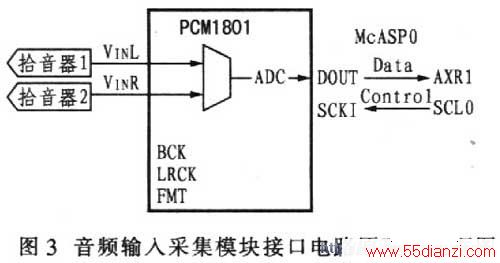

音频输入采集模块由2个PCMl801U型音频采集电路及其外围电路组成,主要功能是对由拾音器采集输入的模拟音频信号进行采样,然后将其转换为DSP可以处理的数字音频数据格式。PCMl801U是采用5V工作电压的双声道16位音频模/数(A/D)转换器,包括1个单端-差分模拟前端、1个5阶△一∑调制器(64倍重复取样)、1个内部高通数字均分滤波器。

DM642视频口0、l中的剩余部分(VPO/B、VPl/B)配置为McASP,与1个PCMl801U连接,实现音频的输入采集功能。用PCMl801U的左、右2个16位音频声道获取4路音频通道的数字化数据,音频采集的数据格式为每路单声道、44.1 kHz采样率,每个采样数据用8位量化。采集输出的数字音频数据通过McASP传给DSP的输入缓冲区单元,当设定用于存放音频采样数据的缓存器满时产生DMA中断,并在DMA中断服务程序中根据实际设定情况处理音频数据,经过实时编码压缩后的音频数据存储到外部SDRAM中。DSP通过I2C总线实现对音频采集电路的编程,以控制采样速率、音频源、音量等具体参数。硬件电路需要提供音频采集电路需要的工作时钟,笔者使用的时钟是11.2896 MHz。音频输入采集模块接口电路原理功能框图如图3所示。

3.3 核心DM642 DSP模块

核心DM642 DSP模块由1个 TMS320DM642 型数字媒体处理器及其外围电路组成,主要对采集到内部输入缓存的数字音、视频数据流进行处理及压缩。视频图像信号的压缩一般属于有损压缩,同时系统又必须满足编码的实时性,所以采用定点DSP可较好地满足整个压缩系统对精度和速度的要求。该板卡设计采用的DM642是专门为图像视频领域的应用而设计的,有完备的片外接口,能够比较方便地扩展片外存储器等外设。

本文关键字:硬件 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术