![]()

其中,SCLK是DSP系统的时钟频率,Divisor的值介于1~65536,可以由timer寄存器相应的值得到,满足关系式

![]()

在BF561的初始化设置中,将UART设为8bit数据模式,同时将Timer2设置为WDTH_CAP模式,用Timer2去捕获串口的数据变化率,而Timer2位于TMRS8寄存器里,程序初始化代码如下:

*pUART_LCR = WLS(8);

*pUART_MCR = LOOP_ENA;

*pTMRS8_DISABLE = TIMDIS2;

*pTMRS8_STATUS = TRUN2 | TOVL_ERR2 | TIMIL2;

*pTIMER2_CONFIG = TIN_SEL | IRQ_ENA | PERIOD_CNT | WDTH_CAP;

*pTMRS8_ENABLE = TIMEN2;

*pUART_GCTL = UCEN;

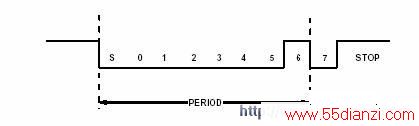

在程序一开始,就会按照初始化设置进行自动波特率检测。当有字符输入时,timer会测量连续2次下降沿的宽度,并返回到timer所对应的period寄存器里。比如说,如果发送 ”@”(0x40h )作为自动波特率检测,发送时包括起始位,总共为8bit,如图10所示。

图10 自动波特率检测字符 ”@”(0x40h )

此处period的大小如上图所示,捕获的UART bits为8位,所以得到

![]()

再根据波特率的公式,就可以求得波特率的大小。此段程序代码如下:

Period = *pTIMER2_PERIOD; //返回period的值

Divisor = Period >> 7; //右移7bit就相当于除以16×8

BaudRate = SYSCLK/16/divisor; //得到波特率

结论

整个控制系统是以LCD显示的界面为基础,按提示进行相应的键盘操作。经过测试,该系统各部分工作正常,无相互干扰现象。实时时钟定时精确,可以达到秒级。数字IO输出的波形编码无乱码,定时精度可达毫秒级。RS232接口传输数据时,以高达115200bit/s的波特率传输,误码率小于5%。该控制系统已成功应用于某 雷达 系统的控制子系统。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术