����Ʒ���ּ���������� ���������������һ����TMS320C6x11ϵ��DSP��ͼ���ȡ����������ģ����Ƶ�źŵ�ͳһ�ԣ�ʵ������������б�ģ����Ƶ�ź�����ӿڵ�ͼ���豸��������ͼ����ϵͳ��Ӳ�������������ġ�ͬʱ�������������ṩһ�����ͨ�õ�������Ƶ�ӿڣ�������ӦTMS320C6xllϵ��DSP�Ľӿڡ�����Ƶ���Ҫ����Ҫ���У�

������֧�ֱ���ģ����Ƶ����ӿڣ����ԶԱ���ģ����Ƶ�źŽ���õ�����ͼ������;

�������ڲ�����ͼ������ǰ���£�ͼ��ɼ��ٶȿ죬����һ����ʵʱ��Ҫ��;

������ռ��CPUʱ���٣�ʹ��ͼ��ɼ������ں�̨�������;

����������ͼ��ӿ�ͨ���Ժã�������TMS320C6u1lϵ�к�̨��ͨ�û�����

����1 ���巽�����

����1.1 ������ѡ��

����Ŀǰ������ģ����Ƶ�ź���Ҫ�ķ����У�����A/D����ģ����Ƶ�źźͲ���ר�õ�ģ����Ƶ�źŽ�����������ǰһ�ַ�����Ҫ���ⲿоƬ���٣�ֻ��A/Dת��оƬ����;������Ҫռ�ô�����CPUʱ�䣬�ڲɼ�ͼ��Ĺ�����CPU����û�ж����ʱ�䴦��ͼ���������ͨ���ᵼ��ͼ����ϵͳ����ͼ���ʱ�����ز��㡣��һ�ַ�������ר�ŵ�ģ����Ƶ�źŽ���������ҪһЩ����Ľӿ�оƬ�����ǿ��Խ�Լ������CPUʱ�䣬ͼ��ɼ����̿���ȫ���ں�̨��ɣ������ϲ���ҪCPU�ĸ�Ԥ������ŵ����ͼ����ϵͳ���ر����㷨�Ƚϸ��ӵĴ���ϵͳ(������Ƶ ���ϵͳ )���ŷdz���������������Ա������������ú��ߡ�

������������һ���ѵ��ǣ���ģ����Ƶ�źŽ���ó���������Ƶ�ź��������dz�����������ʵʱ��Ƶ�źţ����������������Ҳ�dz���;�����෴��DSP�ⲿ �洢�� �ӿڵĶ�������ȴ�Ƚ�����Ϊ�˽��������⣬��������ȡ�����ֻ��巽ʽ.������ʹ�ø���FIFO�������ݽ����ݴ��Ի����ٶ��ϵIJ��죬���������Ļ��廹������ƽ������֮����ٶȲ��졣

���������ڱ������������“���в���”��˼�롣ͨ�������в�����ʹ�÷ֱ����½�������ÿ���в���һ�����ݣ���ʹ��ͼ��ֱ�����ϵ������½���ԭ����1/4���ⲻ�������ϣ���ģ�����Ϊ�˱�֤ͼ��ķֱ��ʣ�������ڸ��в�����ͬʱ����һ����ͼ��������ݽ����ֶ�β�����Ȼ����������ϳ�һ��������ͼ�����������˻����ٶȲ�������ã��ֱ�֤��ͼ��ķֱ��ʡ�

���������ȷ����˼·�ǣ�����FIFO���ݴ�һ��ͼ�����ݣ���Ƶ������ֱ����FIF0��д��ͼ�����ݡ���FIFO��д������Чͼ�����ݺ���CPLD��DSP�����ж�����;ͬʱ��DSP�ӵ��ж����������DMA��ʽ��һ��ͼ�����ݴ�FIFO�ж��뵽���ⲿRAM�д�š�CPLD��Ҫ���“���в���”��ʵ�֡����ƽ�������FIFO��д�������Լ�DSF��FIFO�ж������ݡ�

�������⣬������Ŀǰ��Ҫ�����PAL��ʽģ���źŵġ�PAL��ģ���źŴ����ͼ������СΪ720×576���ء�����������Ҫ��Ըø�ʽ����Ƶ�ź�չ���������Ҫ��NSTC��������ʽ��Ƶ�źŽ��룬ֻ��Ҫ����������һЩ�ļ��ɡ�

����1.2 ϵͳ��ͼ

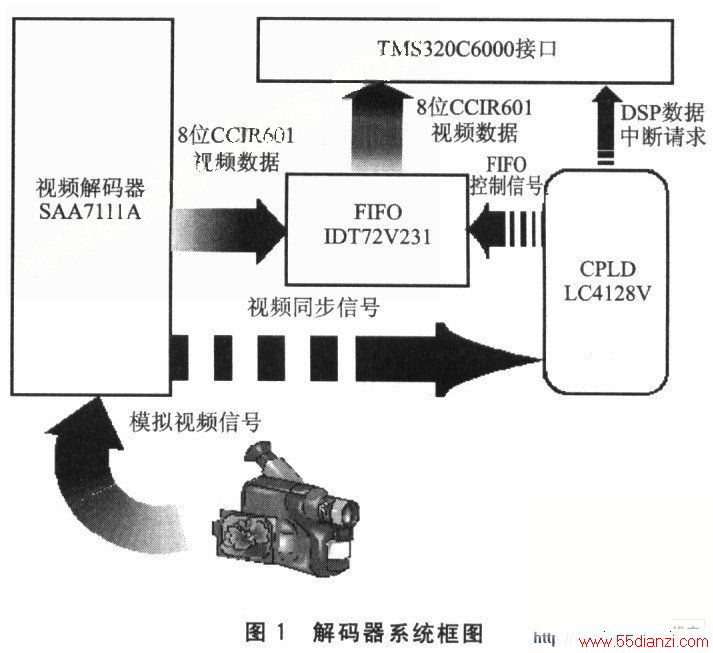

�����ڱ������У�ģ����Ƶ�źŽ��������õ��� Philips ��˾�� SAA7111A ������PAL��ʽģ����Ƶ�źţ�l��ͼ��������720������;ͬʱ����YUV����������4��2��2������������Ҫ 1440 �ֽڵĴ洢�ռ�洢1�����ݡ����ڱ���������Ҫ�õ�FIFO��1�������ݴ棬����FIFO�Ĵ洢��ȱ������1440�ֽڣ����ѡ������FIFO����IDT��˾��IDT72V23l�������2K×9λ�Ĵ洢��ȡ�ͬʱ��ʹ����LaittICe��˾��CPLD—— LC4128V ����Ϊ�м����ӿڿ���“���в���”����ɡ���������FIFO��д�����Լ�DSP��FIFO�Ķ�������ϵͳ��ͼ��ͼl��ʾ��

����2 Ӳ���������

����2.1 оƬ����

����������ѡ��SAA7111A��Ϊǰ����Ƶ��������SAA71llA��Ƶ��������˫ͨ��ģ��Ԥ���� ��· ���Զ�ǯλ��������Ƶ�·��ʱ�Ӳ�����·�����ֶ��������������/�Աȶ�/���Ͷȿ��Ƶ�·����ɫ�ռ�������ϣ���һ������Ƶ���Ƶ��������SAA711lAֻ��Ҫ��һ�� 3.3V ��Դ���磬��C6x11��I/O��ѹһ �¡�SAA7111A����CVBS(������Ƶ)�� S-video ģ����Ƶ���룬���Խ�PAL��SECAM��NTSCģʽ�IJ�ɫ��Ƶ�źŽ���ΪCCIR-60l/656���ݵIJ�ɫ���ַ���ֵ����������ͨ��I2C�ӿڿ��ơ�

����SAA7111A����Ҫ�����ص����£�

������4·ģ������һһ4·CVBS��2·Y/C��1·Y/C��2·CVBS;

��������ͨ����̬����ɱ�̣��Զ��������ѡ���CVBS��Y/Cͨ��;

������2��8λ��ƵCMOSģ�� ת���� ;

������Ƭ��ʱ�Ӳ�������ֻ��Ҫ 24.576 MHz��һʱ������;

�������Զ�̽��50 Hz��60 Hz��Ƶ���Զ���PAL��NTSC�����л�;

���������Դ���PALBGHI��PALN��PAL M��NTSC M��NTSC N��NTSC 4.43��NTSC-Japan��SECAM�źš��������ص���Կ�����SAA7111A����ǿ������ȫ�棬�������������Ƶת����������Ҫ����ȫ���ϱ�ϵͳ��Ҫ��SAA7111A�Ѿ��ڸ�����Ƶ����ϵͳ�еõ��㷺��Ӧ�ã����������ѵõ���ֵ�֤��������SAA7111A���кܸߵ��Լ۱ȡ�

����2.2 DSP��FOFO�ӿڼ���

����TMS320C6xll���ⲿ�洢���ӿ�( EMIF )�ṩ�˹���ʮ��ǿ����ⲿ�ӿڣ�����ʵ�����������Ĵ洢������ӿڣ���SB SRAM �� SDRAM ��SRAM��ROM�ȵȡ��������FIFO�Ľӿڲ�����������������ӿڣ���Ҫ����һЩ�ⲿ������������֮���ʱ��

�����������в��õ�FIFOһһIDT72V23���DZ���ͬ��FIFO���������������Ķ�дʱ��——RCLK��WCLK;ͬʱ�����ж�д�����ź�WENl��WEN2��REN1��REN2��

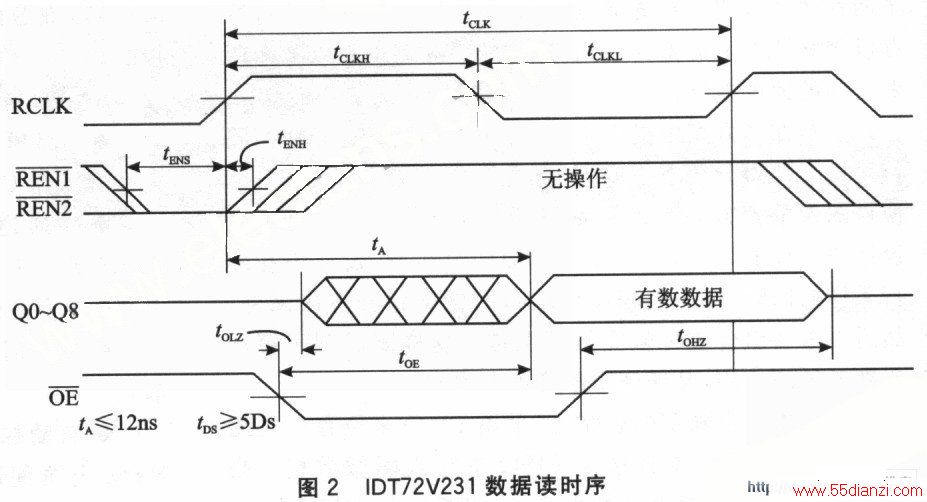

�������ڱ���ƶ��ԣ�Ҫ��DSP��FIFO�н����ݶ������ʹؼ�����DSP��IDT72V23l�Ķ�ʱ��ͼ2��IDT72V31���ݶ�����ʱ��

����ͼ2�У�tENSΪREN1(REN2)����̽���ʱ��(SETUP)��tDSΪ���ݵ���̽���ʱ��(SETUP)����ͼ2���Կ��� IDT72V231 ��һ��SRAM��ʱ���һ���ܴ������ǣ���RCLK�����ص����Ժ���Ҫ��һ���Ƚϳ�����ʱtA�Ż�����Ч���ݳ����������ϡ���ǰһ��ʱ���������ϵ������Dz��ȶ��ģ����Ҹ���ʱ��ɴﵽ12ns��

�������Ƕ���TMS320C6x11���ԣ����ݵĶ�������ARE�źŵ���������ɵģ���������Ƶ���Ҫ���}��FIFO��RCLKʱ�������ṩ��������в��õĽ���취���£�

����RCLK=!(ARE)

����REN1&REN2=CEx+AOE+Address

����Ҳ����˵��RCLK����DSP��ARE�ź�ȡ���õ��ģ���REN1��REN2�ź�����DSP��AOE�źž�����ַ������ṩ��������Ƶ�TMS320C6xll��FIFO�ӿ�Ϊ�����FIFO����ʱ���Ҫ������Ҫ��DSP�Ķ�ʱ��(��Ҫ��Setup/Strobe/Hold����ʱ���)��������Ҫ��

����Setup≥(tENS+tSKEW)/tcyc

����Strobe≥(tA+tDS)/tcyc

����Strobe≥(tCLKH(min)/tcyc

����Hold+Setup≥(tCLKL(min)/tcyc

����Setup+Strobe+Setup≥(trc(min)/tcyc

������ʱ��ͼ�ϵ����ݿ��Կ�����tENS≥5ns��tA≤12 ns��tDS≥5 ns;ͬʱ������IDT72V23l��Ҫ��RCLK�ߵ�ƽʱ��(tCLKH(min)���ڵ���8ns��RCLK�͵�ƽʱ��(tCLKL(min)���ڵ���8 ns�Լ���д����(trc(min)������ڵ���20ns������һ�������࣬��������Եõ���

����Setup≥20ns

����Strobe≥30 ns

����Hold≥l0ns

�����ڱ���Ƶ� TMS320C6211 ��ϵͳ���ϣ�EMIF���ⲿʱ��Ƶ����100 MHz������tcyc=10ns���������Եó�DSP��CExCTL�Ĵ�����Setupֵ����Ϊ2��Strobeֵ����Ϊ3��Holdֵ����Ϊ1��

����ʵ��ϵͳʵ��֤����ͨ��������Ӳ���ӿ���ƺ�TMS320C621l���Ժ��ȶ��ش�FIF0�ж������ݡ�

����2.3 ���������

��������DSP�ӿ���FIFO�Ľӿ��ٶ�ֻ�ܴﵽ15MB/s���ٶȣ�ͬʱ��DSP��ͼ�����ݴ�FIFO�ж������Ժ���Ҫ�����ݴ������ⲿ�洢���У�����DSP��FIFO�Ľӿ��ٶ�����ȫ�����ܸ��Ͻ�����SAA7111A����Ч��������ٶ�(���19.8 MB/s)�ģ�����DSP��ʵʱ�ش���Ƶ����ץ��һ��������ͼ�� ��ˣ���DSP��SAA711lA�Ľӿ�֮����ø���FIFO���л����ͬʱ������ȡ��“���в���”�ķ����������ٶ��ϵIJ��졣ͨ������ó�DSPÿ��4����Ч��Ƶ�źŲ�1����Ƶ�����Ǻ����ġ�(��DSP����ȡ�����ݴ������ⲿ�洢��������Ҫ��ʱ�俼�����ڡ�)

����“���в���”�Ľ���ᵼ������ȡ��ͼ��ֱ�ֱ����½�(����PAL��ʽ��Ƶ�ź���ԭ����576��/���½���144��/��)��Ϊ�˱�֤ͼ��ķֱ��ʣ�������н�ÿ��ͼ��ֳ�������4�β���.��������4�β����У��ֱ�ץȡͼ���в�ͬ��144�����ݣ�Ҳ����˵������DSPץȡ1����������(720×576)��С��ͼ����Ҫ��4�λ�ȡ��Ȼ�������������ϵõ�������ͼ��PAL���ź��ǰ���50Hz�ij�Ƶ��ͼ���������ģ���ÿ���ֿ��Դ���25��ͼ����������“���в���”��ԭ��DSPÿ���ӿ��Դ�PAL���ź��н����6.25�����������С��ͼ������ٶ���ȫ��������ܶ�ʵʱϵͳ��Ҫ������Ƶ���ϵͳ��

����“���в���”���ܵľ���ʵ������CPLD���SAA7111A�����ͬ���ź�(��ͬ������ͬ���ź�)����ɵġ�����IDT72V231(FIFO)��д�������ͨ��WEN�ź���ɵģ����CPLD����ͨ������WEN�ź���ʵ��ͼ��ĸ�����һ����������WEN�źŵIJ�������ͼ3��ʾ��

���Ĺؼ��֣�������ϵ��ʽMSP430��Ƭ������Ƭ��-�����豸 - MSP430��Ƭ��

��һƪ��MSP430��Ƭ����������