LED芯片封装缺陷检测方法(2)

点击数:7251 次 录入时间:03-04 11:53:18 整理:http://www.55dianzi.com 电工文摘

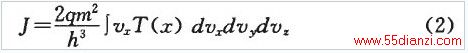

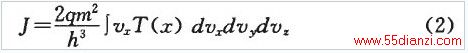

1.2封装缺陷机理 LED芯片受到腐蚀因素影响或沾染油污时,在芯片电极表面生成一层非金属膜,产生封装缺陷[11]。电极表面存在非金属膜层的LED芯片压焊工序后,焊接处形成金属一介质-金属结构,也称为隧道结。当一定强度的光照射在LED芯片上,若LED芯片失效,支架回路无光电流流过若非金属膜层足够厚,只有极少数电子可以隧穿膜层势垒,LED支架回路也无光电流流过;若非金属膜层较薄,由于LED芯片光生电流在隧道结两侧形成电场,电子主要以场致发射的方式隧穿膜层,流过单位面积膜层的电流可表示为。

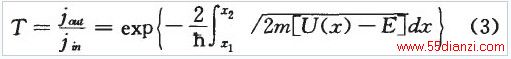

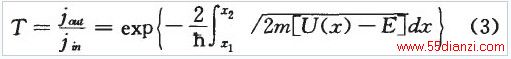

其中q为电子电量,m为电子质量,矗为普朗克常数,vx、vy、vz分别是电子在x、y、z方向的隧穿速度,T(x)为电子的隧穿概率。又任意势垒的电子隧穿概率可表示为

其中jin、jout。分别是进入膜层和穿过膜层的电流密度,

x指向为芯片电极表面到压焊点,为膜层中z方向任意点的势垒,E是垂直芯片电极表面速度为vx电子的能量。

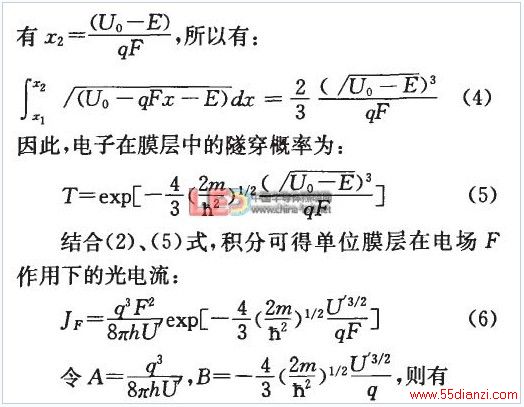

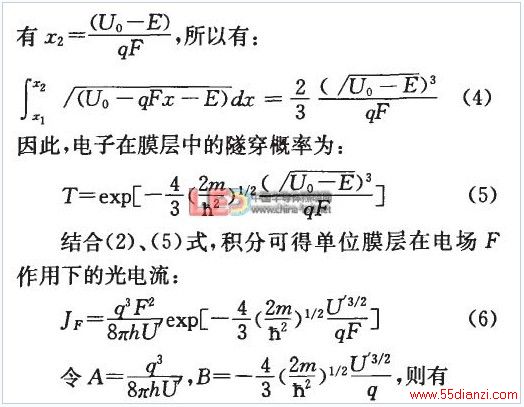

图2为在电场f’作用‘F芯片电极表面的势垒图,其中EF为费米能级,U''为电子发射势垒。由图2,若芯片电极表面为突变结,其值为U0,光生电流在隧道结两侧形成的电场强度为F,电极表面以外的势垒为U0-qFx。取芯片电极导带底为参考能级E0(x=0),因而有x<0处,U(x)=0;x>0处,U(x)=U0-qFx,根据条件U(x)=E=U0-qFx2

式中d为膜层厚度,V为膜层隧道结两侧电压。当LED芯片发生光生伏特效应时,由式(7)可知,流过芯片电极表面非金属膜层的电流受到膜层厚度的影响,随着膜层增厚,流过膜层的电流减小,流过LED支架回路的光电流也将减小。

综上所述,引脚式LED支架回路光电流的有无或大小可以反映封装工艺中LED芯片的功能状态及芯片电极与引线支架的电气连接情况,因此,可以通过检测LED支架回路光电流达到检测引脚式封装工艺中芯片功能状态和封装缺陷。

本文关键字:检测 LED芯片 电工文摘,电工技术 - 电工文摘