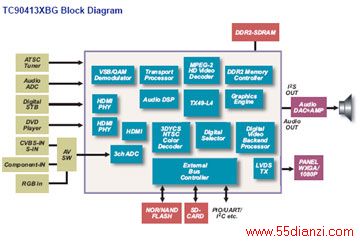

��֥��˾��TC90413XBG��ר������ATSC LCD HDTV��Ƭ��ϵͳ��SoC�����������˴ӵ�г�������LCD��ʾ���ӿڵ������ź�ͨ·�����⣬TC90413XBG��֧��Ϊ�˸Ľ���Ƶ�����ĸ����㷨�������õ�һ��16λDDR-2�ӿھ���֧��ͳһ�Ĵ洢���ܹ��������ж���ڲ���������ж����MIPS CPU�����Ӹ����Ӧ�ù��ܡ����Ľ�����TC90413XBG����Ҫ���ܣ������Լ�����ͼ��

TC90413XBG Single-chip SoC for ATSC LCD TV

������

The TC90413XBG is targeted for ATSC LCD TV applications and integrates the entire signal path from the tuner output to the LCD panel interface. Compared to previous Toshiba chips, it integrates more functional blocks on chip reducing system cost. In addition it supports an extensive set of algorithms for improved video quality. It supports a unified memory architecture requiring only a single 16-bit DDR-2 interface. The device has multiple internal processors to offload the main MIPS CPU for value-add applications.

This new SoC TC90413XBG features a level of integration previously unseen in SoCs intended for use in designing mass market HDTVs for the North American market. The TC90413XBG IC incorporates MPEG-2 HD video and Dolby ® Digital audio decoding, a 64-bit 333 MHz MIPS processor, dual HDMI 1.3 ports and a back-end processor capable of driving both WXGA and 1080p display in one chip. Additionally, the TC90413XBG is available as part of TAECs new Customizable Universal DTV Platform (CUDP) for digital television applications, a platform-level solution, which was also announced today, that includes ready-to-manufacture hardware and production software to provide OEMs with a complete HDTV system that is fully customizable to support different international standards and markets.

��Ҫ���ԣ�

333 MHz TX49/L4 MIPS RISC core

�C 8 KB each I & D cache

�C DDR-2 DRAM controller(16-bit 400 MHz)

VSB/QAM demodulator

�C Compliant to ATSC 8-VSB and 64 and 256 QAM

Transport stream processor

�C Compliant with ATSC and cable standards

Video decoder

�C MPEG-2 MP@HL decoder

�C Processes all ATSC and cable formats

Audio processor

�C Dolby digital decoder

�C I2S inputs and outputs

�C SPDIF output

HDMI inputs

�C Dual port

�C HDMI 1.3 compliant

�C Deep color support

�C High Definition Content Protection (HDCP)

Analog video interface

�C Composite and S-video input (3D comb filter)

�C Component video/RGB interface

LVDS output

�C Supports LCD/PDP panels up to 1920 x 1080p

Video processing

�C 3D motion adaptive de-interlacer

�C MPEG-2 noise reduction

�C Color management

�C Tone correction

�C Edge enhancement

�C Dynamic contrast

Interface and peripherals

�C SD card interface

�C Nand flash memory controller

�C 8/16-bit local bus to attach other peripherals with DMA

�C UART/SIO

�C I2C bus

�C General purpose I/O pins

Package

�C PBGA 456 pin 27 x 27 mm and 1 mm pitch

���ƣ�

Highly integrated Systemon-Chip (SoC) for ATSC LCD TV applications

Chip integrates VSB/QAM demodulator, MPEG-2 HD processor, Dolby® digital decoder, dual HDMI 1.3 ports, 64-bit MIPS CPU, analog video receiver including 3D YC

separator and ADCs, LVDS drivers for both WXGA and 1080p TVs.

Extenstive video enhancement functions include motion adaptive 3D interlace to progressive conversion, edge enhancement, color management, dynamic contrast, tone correction, and transient improvement

High level of integration reduces the number of components on the TV board, reduces cost and improves reliablity

Turnkey solution for ATSC LCD TV available

Uses only a single DDR-2 800 DRAM chip to support a 1080p panel

Package: 456-pin PBGA

���Ĺؼ��֣���֥ �繤��ժ���繤���� - �繤��ժ