板级电路的可测性设计,是使电路模块易于测试的设计,是以改善电路模块可测性和可诊断性为目标的设计,是不改变原来电路的功能,尽量少用附加的硬件,力求用简单方法测试被测对象的一种设计方法。目前国内外前沿的可测试性设计技术大部分是从武器装备和大规模集成电路的测试需求发展起来的,是系统级或芯片级的可测试性设计技术。而电路板可以看作是一个小系统的缩影,也可以看作是芯片电路的扩展,因而一些系统级、芯片级的可测试性设计和测试方法可以应用到电路板的可测试性设计中。 一、边界扫描技术

自从边界扫描标准出现以来,市场上支持边界扫描机制的芯片及设计开发软件与日俱增,应用越来越广泛,逐渐成为主流可测试性设计技术。边界扫描机制提供了一种完整的、标准化的可测试性设计方法,其主要思想是:通过芯片管脚和芯片内部逻辑电路之间,即芯片的边界上增加边界扫描单元,实现对芯片管脚状态的串行设定和读取,从而提供芯片级、板级、系统级的标准测试框架。

边界扫描机制可以实现的目标:①测试电路板上不同芯片之间的连接;②测试芯片及电路板的功能;③应用边界扫描寄存器完成其他测试功能,如伪随机测试、特征分析、低速静态测试等。

在设计过程中主要考虑以下几方面的问题:

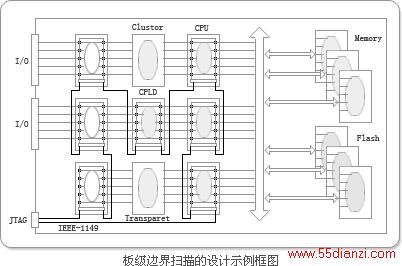

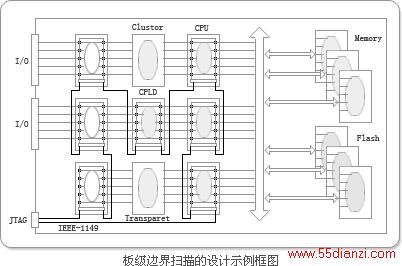

1、在器件的选择上要尽量选用支持IEEE-1149标准的芯片,而对于小型芯片,在实现功能相同的前提下,要尽量选用符合IEEE-1149标准的。电路的数字控制部分争取用可编程逻辑器件实现,同时对可编程逻辑器件的选择尽量采用兼容的器件,这样可以有效地对不同厂家的可编程逻辑器件进行同时配置。

2、边界扫描链路是进行边界扫描测试的数据传输通路。符合IEEE-1149标准的板级边界扫描链路的基本连接方式一般有串行方式、并行方式和独立路径方式。在板级电路设计中应根据实际需要来选择合适的测试总线连接方式。JTAG信号在设计时应考虑其工作的稳定性和各自功能的实现。TCK和TMS信号很重要,要保证它们稳定、无歪斜、缓冲、单调。TCK、TMS在进行测试时其典型扇出不能多于10个,为保证信号的完整性及电路的可靠性,一般在扇出大于5个时应进行缓冲驱动处理。对于不同工作电压系列的芯片在进行测试总线的串行或并行连接时,要把电路板上器件归类,不能将芯片的JTAG信号直接相连,应进行电压转换以便电压兼容。为了能将电路板级的测试和可编程器件的在线编程有机结合而又互不干扰,就要解决测试与在线编程或在线仿真的兼容问题。技术途径上可以采取在结构设计时设置选择开关,同时在软件代码中编写相关的开关控制程序。

3、对于一个电路板系统,若其上都是边界扫描器件,则只要将器件的TD1、TDO依次首尾相连,优化设计边界扫描链即可对整个电路板进行测试。但是往往一个电路板系统包含许多非边界扫描器件。一般可将非边界扫描器件分成几组,通过在电路板上置入边界扫描结构器件,包围非边界扫描电路来实现对每组非边界扫描器件的测试,此方法称之为簇(cluter)测试。由IEEE-1149兼容器件向被测器件注入测试向量,同时采样ASIC边界扫描寄存器中的结果数据,从而进行响应分析。

边界扫描技术在解决高密度电路板的测试有较大优势,但它在电路的动态测试和性能测试方面表现出一定的局限性。因而,有必要应用其他的可测试性设计技术弥补边界扫描技术的缺陷。 二、BIST(内建自测试)技术

BIST技术是针对芯片内部功能测试发展而来的,将其应用到板级模块可测试性设计中用以提高电路板功能测试的可测试性。与电路常规测试相比,基于BIST设计的电路非常有利于故障诊断、维护测试和开机测试。

BIST方法可分为两类,一类是在线BIST,另一类是离线BIST。在线BIST包括并发和非并发的方法,测试在电路的正常功能条件下进行,不把被测电路置于测试的方法。采用并发在线BIST方式时,测试与电路的正常操作同时进行,常用在编码和比较电路中。采用非并发在线BIST方式时,测试在电路空闲状态进行,常用在故障诊断中,测试过程可以随时中断,电路的正常功能可以重新开始。对于离线测试,测试不在电路的正常功能条件下进行,可以应用在系统级、板级和芯级测试,也可以用在制造、现场和操作级测试,但不能测试实时故障。

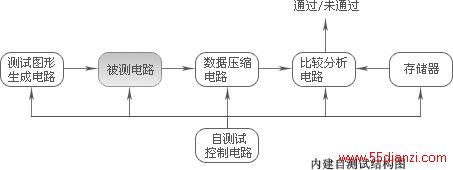

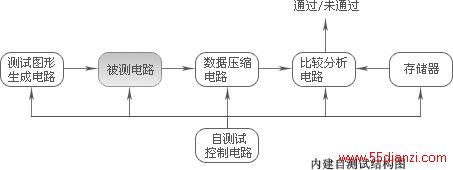

内建自测试包括测试图形生成电路、数据压缩电路、比较分析电路、存储器和控制电路。其自动产生测试向量,自动判断结果通过还是未通过,简化了外部测试设备。测试生成电路所产生的测试图形在时钟作用下加到被测电路CUT上;为了减少测试响应数据所用的空间及易于分析,常常把响应数据压缩,数据压缩电路的功能就是把测试响应数据压缩成特征符号;比较电路把捕获到的响应特征符号与参考特征符号相比较,最后给出结果:通过还是未通过;所有的测试操作,包括测试开始、检测结束以及同步都由内测试控制电路控制。

被测电路可以是组合电路、时序电路、存储器和其他类型的电路,也可以是电路模块。对于时序电路,测试图形施加前应确定初始状态,另外应按照电路或系统的具体机构,尽可能采用各种方法使得测试电路最小化。

BIST所用的测试图形生成器(TPG)常见的形式有两种,一种是伪随机图形生成器(PRPG),它采用的是多输出线性反馈移位寄存器;另一种是移位寄存器图形生成器(SRPG),采用的是单输出的自动方式线性反馈移位寄存器。为了简化问题,也可以把PRPG看做并行随机图形生成器,而把SRPG看做串行随机图形生成器。BIST所用的输出响应分析器(OSA)常见的形式也有两种,一种是多输入特征分析寄存器(MISR),另一种是单输入特征分析寄存器(SISR),它们采用的都是线性反馈移位寄存器。

针对电路板的性能测试,BIST技术是一种很好的解决方案。但是板级BIST不可能完成全面的性能测试工作,必须深入了解具体被测对象,从而提出有针对性的和典型代表意义的测试方法。 三、应用实例

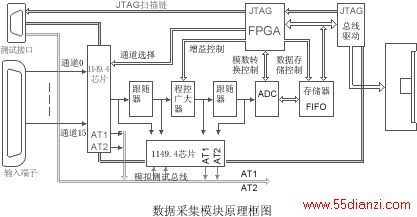

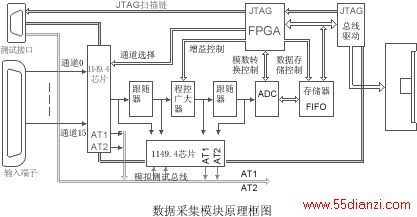

以一个数据采集模块为被测对象,采用内建自测试技术和边界扫描技术制定可测试性设计方案。该方案中不引入扫描控制器,而是采用在FPGA内构造扫描控制器的设计策略,由FPGA控制自测试的时序和调度发生在每一个阶段的测试操作,并读出响应结果。

在可测试性设计前,先对整个电路板进行模块划分,即分为模拟电路模块、数字逻辑电路模块和存储器模块。对数字逻辑和存储器模块来说,其测试代码由大量的测试向量组成。对于模拟模块,由于其输入和输出端点数量较少,所以一旦建立了测试访问路径之后,外部测试仪就可以有效的施加测试。

在电路板中,建立了由IEEE-1149标准器件组成的数模混合扫描链。测试时,电路板被置于BIST模式下,FPGA控制测试的整个过程。经过扫描路径,DSP、FPGA等都可以被测试。在测试非边界扫描芯片时,测试输入芯片被配置到伪随机图形发生器(PRPG)模式,测试输出芯片被置于多输入特征寄存器(MISR)模式,一旦测试运行开始,测试产生的特征值用于验证非边界扫描芯片电路是否正确。

在该电路板上用虚拟探针实现了对模拟信号(如电压)节点的检测;用模拟测试总线代替了电路内测试仪,其中可探查混合信号芯片中不同的数字和模拟部件;对连接到芯片管脚的各种外部阻抗进行了电子访问。采取的技术途径是用模数混合边界扫描专用芯片来模拟通道开关,所加的测试激励来自模拟信号专用测试总线。在测试模式下,根据不同的测试点以及通道开关所处位置,按照一定的测试顺序,逐级分块测试,可以逐步诊断出故障。每个测点都挂在通用总线上,并在JTAG管理下将总线上的信号加载不同的测试点。

在测试过程中,我们可以全面了解被测PCB功能模件中各芯片之间的互连情况和芯片本身的内部故障,如测试FIFO的地址线、数据线互连,我们采用的是基于边界扫描的簇测试方法;而对其逻辑功能的测试,我们构建简单的BIST电路,通过比较存储器输出数据和期望的正确标准值是否有差异来判断FIFO逻辑故障。从测试结果可以看出将边界扫描技术、BIST技术结合可以发挥更好的测试效果。

本文关键字:电路板 电工文摘,电工技术 - 电工文摘