在DSSS系统中,速率为rb bps的二进制随机数据与一个速率远高于它的伪随机码相乘,则频带被展宽。相乘之后得到的二进制伪随机(PN)输出符号叫做码片,其速率称为切谱率,为rc码片/秒(cps)。码片是一个随机的与噪声类似的信号,因此又叫做PN信号,其速率决定了被发送的扩频信号的带宽。通常码片速率远高于数据源的比特率,而二者之间的比值就是处理增益(PG)。PG真实地反映了在接收端解扩(去掉PN码)前后信噪比的改善情况。

DSSS系统的接收机必须首先去掉接收信号的扩频码(即解扩),然后才能对信号进行解调。解扩时,接收机必须产生一个与发端PN码完全一样的伪随机解扩信号,该信号的相位也必须锁定在发端PN码相位上。芯片组之中的HSP3824的码捕获和码跟踪环路可以实现这一功能,而收、发端PN码相位的精确对准则是由相关技术实现的。

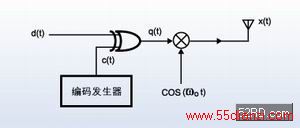

DSSS发射机

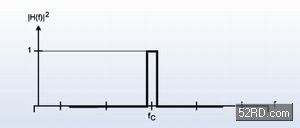

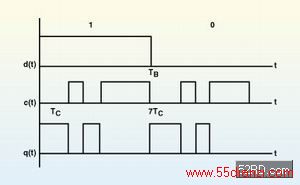

DSSS发射机原理如图1所示。图中用d(t)表示数据,c(t)表示扩频码,扩频之后的信号q(t)被送到BPSK调制器中去,该调制器工作在载波频率fc上,扩频调制后被发射的信号用x(t)表示。

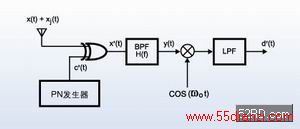

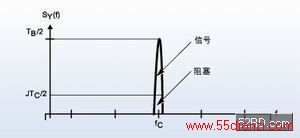

在课本中常见到图2所示的DSSS接收机概念图。值得注意的是,该框图所示的接收系统是在射频部分直接进行解扩,而本文所要介绍的PRISM芯片组则在基带通过使用HSP3824芯片进行解扩。故图中所示的例子只能用来说明解扩的概念,并不能反映在实际中PRISM的解扩实现方法。

该例中,接收信号包含由发端过来的经过扩频调制的信号x(t)和一个窄带噪声xj(t)。如果本地产生的解扩序列c’(t)与发端的扩频码c(t)相同,那么解扩后的信号通过带通滤波后解调,得到的d’(t)应与发端数据d(t)相同。

处理增益的好处

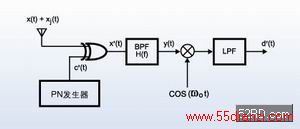

处理增益带来的最大好处就是提高了DSSS信号的抗干扰性能,因为PN码扩展了发端信号的带宽,将信号的功率分散到整个扩频带宽内,所以降低了窄带干扰对系统的影响。实际上,DSSS系统的接收机在将有用信号解扩的同时也对干扰信号进行了扩频,见图3。

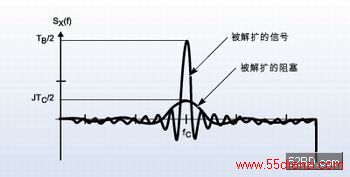

图3给出了接收机输入信号功率谱密度(PSD)函数、解扩信号的PSD函数、带通滤波器的功率传输函数及其输出信号的功率谱密度,该图直观地描述了处理增益对干扰的抑制作用。

解扩前,干扰的频带很窄,但具有很高的PSD峰值,而DSSS信号频带很宽,且PSD 较低。解扩操作拓宽了干扰的频带,将窄带干扰的能量扩展到较宽的频带中去,降低其PSD值,也就减小了干扰功率对系统性能的影响。从BPF的输出可以看出解扩对提高系统信噪比的作用。

例如,有一个系统使用BPSK调制,并要求解调前信号的信噪比至少为14dB才能保证误码率性能,那么如果在该系统中引入10dB的扩频处理增益,则由14dB-10dB=4dB可以推出:接收机在接收信号的功率与噪声功率相比只高4dB时仍然能够获得所要求的性能。

一般来说,处理增益越高,DSSS信号的抗干扰性能就越好。处理增益的标准定义是10lg(rc/rb),单位为dB。如果系统的数据率为1Mbps,切谱率(PN码速率)为11Mcps,那么根据该定义可以算出系统的处理增益为10.41dB。对此,如果采用PRISM芯片组,那么每一个数据比特将与一个11位的PN码序列进行异或。10.41dB的处理增益也可以看作10lg(11),这里“11”是PN码序列的长度。如果改用长度为16位的PN码来扩频,那么处理增益就等于10lg(16),即12.04dB。

用于DSSS系统的PN码必须具备良好的自相关性、互相关性并保持一定的随机性。DSSS接收机使用一个与发端完全相同的PN码进行相关解扩。

下面讨论几类相关性较好的PN码,主要讨论每周期7个码片和15个码片的巴克码、Willard码以及m序列,这几种码在HSP3824芯片中都可以实现。

1. PN码

具备DSSS要求的数学性能,能够用于DSSS系统的PN码有最大长度序列。

最大长度序列(m序列)的周期为(n为整数),可以由移位寄存器外加或门产生,其形式由产生它的本原多项式决定。m序列不但具有很好的随机性而且具有双值自相关函数特性。

例如,7位的m序列PN码是由本原多项式发生器:

产生的,输出码片如下:0 0 1 0 1 1 1 0 0 1 0 1 1 1 0 0 1 0 1 1 1 0 0 1 0 1 1 10...

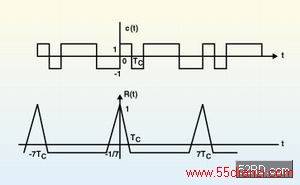

图4给出了数据d(t),由以上m序列构成的扩频码c(t),以及由d(t)和c(t)异或得到的扩频后的信号q(t)。图5给出了这个7位m序列PN码的码形及其自相关函数。值得注意的是,该PN码的自相关函数也是每隔7个码片周期重复一次。如果对每个数据比特采用一个完整周期的PN码进行扩频,那么该自相关函数也就每隔一个数据比特重复一次。

再如,15位的PN码序列由本原多项式:

产生,输出码片如下:

0 0 0 1 0 0 1 1 0 1 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 1 1 10 0 0 1 0 0 1 1 0 1 0 1 1 1 1...

2. 巴克码

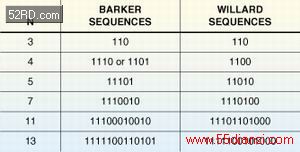

巴克码是一种独特的短码,具有相当好的相关性。这种N位的短码(N=3-13)非常适合DSSS应用,并且都能由HSP3824产生。表1给出了几种巴克码。

3. Willard码

Willard码是通过计算机仿真和优化找到的,在某些情况下它能够提供比巴克码更好的性能。同时,Willard码也和巴克码一样可以由HSP3824产生。表1中也给出了几种Willard码。表1中所给编码的反码也可以用于DSSS,因为它们同样具有DSSS所要求的自相关性。

通过配置HSP3824实现各种PN码扩频,HSP3824是PRISM芯片组中的基带处理器,由它产生PN码序列,通过对HSP3824编程,可以实现最长16位的任意PN码序列。

PN码发生器

在BPSK调制时,PN码序列是从HSP3824内一个可配置的寄存器中并行地读出,以串行方式送给调制器,从而对数据进行扩频的。每一个数据符号都使用同样的PN码扩频。

HSP3824中的可配置寄存器最多可以对16位编程。发端PN码的高、低8位分别在寄存器CR13和CR14中,相应的收端PN码的高、低8位则在寄存器CR20和CR21中。寄存器CR3的第5位和第6位用来设置每个数据比特中包含的码片数。先发送给调制器的是PN码序列的MSB部分,当序列长度不足16位时,将MSB截短。

HSP3824中的PN码相关器是专门针对BPSK扩频应用而设计的,因此它包含两个实数相关器,一个用于I通道相关,另一个用于Q通道相关。相关器需要的收、发端PN码序列以及序列长度都被存入HSP3824的可配置寄存器中,所以发端的扩频参数和收端的解扩参数都可以修改。相关器由时不变匹配滤波器构成,也称为并行相关器。

本文关键字:收发器 电工文摘,电工技术 - 电工文摘

上一篇:8051F020触摸屏驱动控制