1��������

�������������һ�ֽ������ź�ת��Ϊ��λ�ƻ�����λ�ƵĿ�������װ�á������ٶȺͿ��������ϸ�ͬ������Ӧ�ٶȼ��죬�нϸߵ��ظ���λ���ȣ�����Ӧ���ھ��ܿ��Ƶij��ϡ�

�������õIJ����������ϵͳ�����������ƣ�������ʵ���䲽������IJ��������ַ�����������ռ��CPUʱ��϶࣬�����˲�������ٶȵĽ�һ����ߣ�����������ʽ�Ŀ��������ܽϲ��EMI�����صij�����ɿ��Բ��紿Ӳ����·����Ӳ���У����η���������ϵ���ӣ��ô�ͳ�ķ���Ԫ��ʵ�֣���·��ģ�������߸��ӣ�����Բ���Ľϴ���ϵͳ�ɿ���Ҳ�������⡣

����ISP��In��system Programming����������Lattice�뵼�幫˾���������һ���¼��������Դ��ģ�ɱ��������Ϊ���ģ����жԵ�����������·�塢������������ϵͳ�������ܽ��ж�̬�����������������ȡ���������е�74ϵ��оƬ���ɸ�����Ҫ����������Ӳ����Դ����·���ĵͣ���Ӳ���������Ĺؼ���

����������ͳ�ĵ���ϵͳ��ƣ������ԭ��ͼ���룬���̸��ӣ�ֻ�ܴӽṹ�϶Ե�·�����������������Բ�ִ���EDA��ESDA��ƹ��ߣ�������HDL��HardwareDeSCRJPTion Language����Ϊ������룬�����Դӵ�·��Ϊ����ʼ��ģ�����Ч�ʸߣ������ǿ��VHDL�ǹ����ϵ�һ��������HDL��IEEE��1076������VerilogHDL��1995��ʵ�ֱ�������HDL����IEEE��1364������������ʽ�ӽ�C���ԣ���д������������Ч�ʸߣ���֧��ģ����档���������IJ����������ϵͳ���ṹ����������չ�Ժá����ۺ������������غ�Ϳ�����Ӳ����·��

2��оƬ���˼�����

2��1������ܹ�

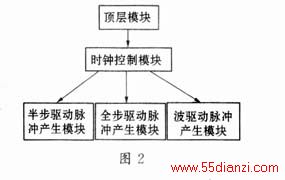

��������оƬ����ģ�黯��Ʒ�ʽ��TOP��DOWN����Ʒ�����

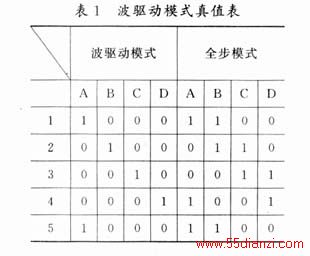

������оƬ����������������ģʽ����������Wave��ģʽ���벽������Half Step��ʽ��ȫ��ģʽ��

����������ģʽҲ��������Ĺ���ģʽ��������ĸ�����ֱ�����ͨ�磻ȫ��ģʽҲ������˫���Ĺ���ģʽ��ÿһʱ�̣����������������ͬʱͨ�磻�벽ģʽҲ��������Ŀ��Ʒ�ʽ�����ֹ���ģʽ�£��������ÿһ���IJ����Ϊȫ��ģʽ��һ�룬�����ھ��ܶ�λ��

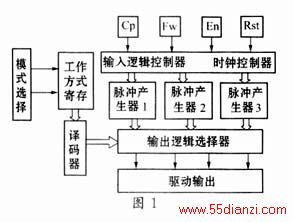

�����������ֹ���ģʽ��оƬ��ģʽ���루mode��ָ���л���оƬ�ϻ���������ת������ƣ�fw������λ���ƣ�rst���ͽ���ͣ�����ƣ�en����оƬ�ṹʾ��ͼ��ͼ1��

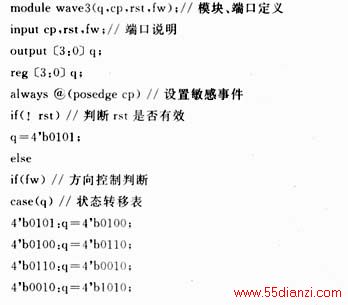

������������벽����ģʽԴ����

�������ϳ����Ƿ�������ƹ���Ҫ���أ�Ϊ�ˣ����DZ�д�˲��Գ�����Active��HDL����ƽ̨�½��й�����֤�����ڸ�ģ�鹦���������ƣ�����ֻ�����벽��

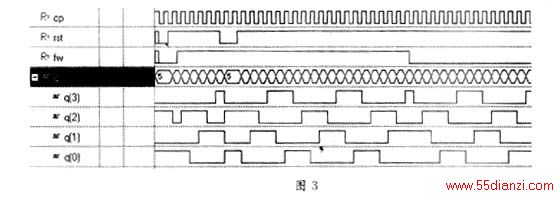

��������沨����ͼ3��ʾ��

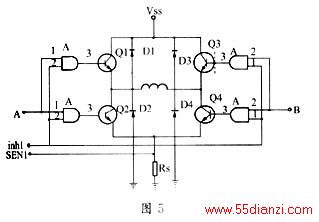

3��4������ģ�����

��������ģ���а��������ѡ������ģʽѡ��λ���ƣ�������Ƽ�ȫ�����������źſ��ơ���ˣ�����ϵͳ����Ҫ�����������е�ģ�飬�Ƕ���ģ�����Ҫ����mode��00ʱ�����Ϊ������ģʽ��mode��01ʱ�����Ϊȫ��ģʽ��mode��10ʱ�����Ϊ�벽ģʽ��mode��11ʱ��err��1�����������Ϊ����̬���������Ϊin1��in2��ȫ��ģʽʱin1��in2�����Ϊ1��

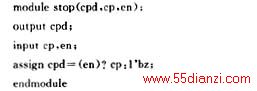

�����������Դ�������£�

�������ݶ���ģ��Ĺ��ܣ���������˸�ģ��IJ��Գ��������˷��档�ɲ��η����ɼ�����ȫ�ﵽ���Ҫ���������mode��10ʱ���벽������������Ρ�������沨�����£�

���Ĺؼ��֣�������� �繤��ժ���繤���� - �繤��ժ