解决新问题的新型控制器

对大多数笔记本电脑应用来说,两相设计可以把电感电流值控制在每相20A或者更低,以便对负载阶跃进行最快响应,并保证最低成本。开关频率设定必须足够高,以便能以所要求的转换速率对负载的瞬态变化做出响应。必须保证MOSFET的RDSON很低,以最大限度地减少高频开关损耗,而且控制器的反馈环路的带宽必须足够高,以确保响应的快速性。不幸的是,老式的控制器的带宽有限。提高开关频率并无裨益,因为很窄的带宽限制了环路响应。电感不能提供很大的电流阶跃,因此需要更多的大电容。这种设计的成本和尺寸非常大,而且限制了实时输出电压的阶跃响应。

新型多相同步控制器可以解决这些问题。它们稳定而高速的反馈回路可以实现尺寸更小、成本更低的设计。有些控制器还支持在较低开关频率下单相工作,从而大大提高低电流和间歇电流条件下的效率。

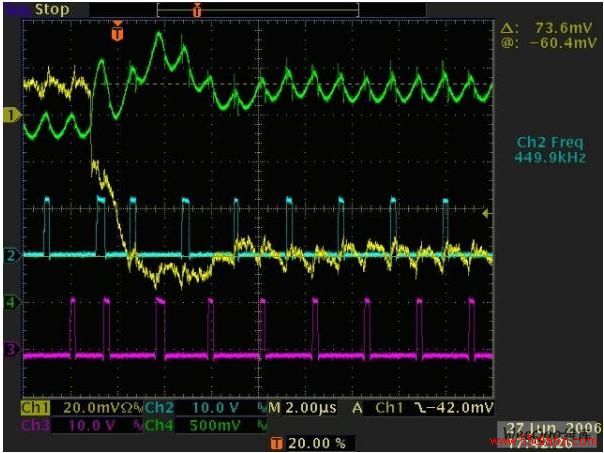

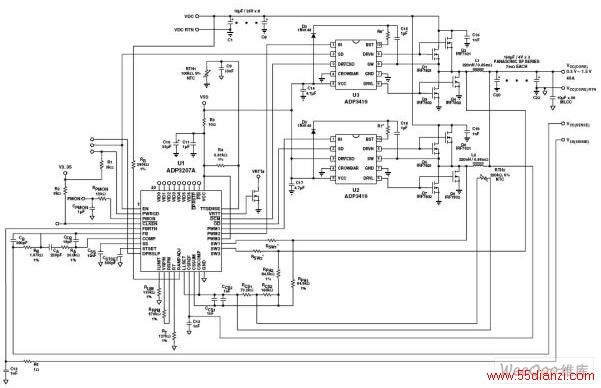

图1:当使用两相电源,ADP3207A和ADP3419对负载阶跃的响应。

若得到恰当的补偿,高带宽控制器可以应对最大的负载阶跃而不会产生振荡。控制器可以通过电感提供更多电流,因此从大电容上取走的电荷量更少。新型的控制器可以快速响应电流瞬态,并同时导通多个相,增加可用的负载电流而无需增加大电容。控制器可以处理很大的负载阶跃,从而让电感、电容和MOSFET的选择简单易行。

确定电感值

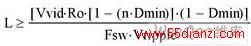

每相数百kHz的开关频率可以保证设计在开关损耗、纹波和输出滤波器的尺寸等方面取得良好平衡。输出滤波器中的电感值取决于纹波要求而非输出电压。

其中,R0是负载电阻,Vripple是所容许的、由于电感纹波电流所引起的纹波电压。电感中的纹波电流峰峰值应该小于其最大DC电流的一半。8A的纹波电流在负载为2.5mΩ的情况下所对应的纹波电压是20mVpp。对两相电源来说,Vvid输出电压为1.115V,FSW=280kHz,由以上公式可以计算出L≥423nH。

电感不应该在每相峰值电流处出现饱和,应该能承受磁芯损耗和平均绕组电流。使用尽可能小的电感可以减少输出电容器的数量。电感的直流电阻会影响许多控制器设计中的电流敏感度,因而需要在功率损耗和测量精度之间取一个折衷的值。

最大限度减少输出电容值

开关稳压器输出端的陶瓷电容和大电容具有不同的作用。陶瓷电容负责处理CPU的高频瞬态过程,将它们放置在CPU插座里面,可以实现最佳的瞬态抑制,但这限制了所放置的电容数量。如果需要额外的电容,则必须将它们放置在CPU插座附近。

最坏的瞬态过程通常是在深休眠状态发生的最大负载阶跃。开关的导通时间、最大输出电流阶跃和最大输出转换速率决定了在CPU电源引脚处的输出滤波器的设计。对大多数笔记本应用来说,输出电容至少为300μF,这可以通过32只并联的0805 10μF陶瓷电容来获得。PCB上寄生参数的变化将导致所需的电容数量量发生改变。

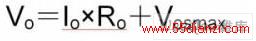

简单地在低频输出滤波端放置一堆大电容,除了成本很高、尺寸很大外并无什么好处。实时的电压变化设定了一个上限值,即电源必须能产生电压跃升,且在给定的时间内稳定到特定的误差带内。输出端还要求输出电容具有最小电容值限制,以便在最大负载阶跃Io条件下和最大可容忍的过冲范围内,保证具有平滑的负载电压。

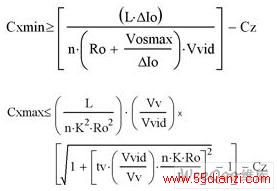

在最大的可容忍过压Vosmax条件下,负载电压是这些方程可以确定大电容Cx的极限值

,其中K=-ln (VERR / VV)。

为了满足上述方程,大电容的等效串联电阻(ESR)应该小于降压电阻Ro的两倍。如果上述方程的求解结果表明Cxmin大于Cxmax,则可以减小电感值,或者增加更多的相,以满足Vvid阶跃要求。若要求在减小电感的同时维持相同的输出纹波,则开关频率应该提高。

例如,若Cz=320μF,实时VID阶跃为22μs、220mV阶跃(tv和Vv),限制过冲电压为27mV,稳态电压误差(Verr)为10mV,则大电容应该在1.1mF到2.1mF的范围内。若采用4个330μF的铝电解电容,且每个电容的ESR典型值为6mΩ,则总的电容值为1.32mF,总的ESR为1.5mΩ。

大电容的等效串联电感(ESL)应该足够低,以便在负载出现阶跃时抑制高频振铃。

ESL=Cz×Ro2×Q2,其中,对于临界阻尼系统来说,Q2被限制为2。

如果大电容的ESL太大了,则可以增加陶瓷电容的数量,或者采用ESL较小的大电容。

MOSFET的选择

降压电源中的MOS功率器件需要具有很低的RDSON,以使导通损耗和功率耗散最小化。它们还要求很低的输入电容,以最大限度减少导通时间。更快且CISS更低的器件具有更高的RDSON,因此需要在这几个指标之间进行折衷。由于采用MOSFET驱动电路,所以栅极驱动电压被限制为5V,这样,具有逻辑电平阈值的MOSFET便成了唯一选择。来自主电流和纹波电流的功率耗散是同步MOSFET功率损耗的主要组成部分。

图2:ADP3207A的电路实例。ADP3207A在处理器选择低功耗工作时,可以变换到单相工作模式。

如果逆传输电容在开关节点变为高电平时将足够多的电荷耦合到栅极上,同步MOSFET可能会意外导通。这会导致主器件和同步器件同时导通的直通现象(shoot-through)。为防止这种情况出现,可以使用一个反馈电容,并使它与同步器件上输入电容的比值为1:10或者更低。

同步MOSFET的关断时间应该小于每相的MOSFET驱动器的非重叠死区时间(dead time)。举例来说,ADI公司的ADP3419 MOSFET驱动器的输出阻抗为1.5Ω,其典型的死区时间为45ns。如果使用一个典型栅电阻为1Ω的MOSFET,并让RC时间常数小于45ns,则总的栅电容值的上限为9,000pF。

当使用两个并联MOSFET时,每个栅电容应该小于4,500pF。

高压端的MOSFET要求能承受导通电流和开关损耗所产生的功耗。开关损耗来自于开关的导通和关断,因此这些FET的输入电容值必须小于同步MOSFET的输入电容值。

需要注意的另一问题是每一相驱动电路的损耗。每个驱动器的总待机功耗加上提供栅电荷时对应的功耗,应该小于驱动器在最高环境温度下的热耗散极限。对于工作在温度可高达90oC的PCB上的 SOIC封装来说,0.5W的总耗散对应120oC的结温。

推荐的输入电容值

高功率侧的MOSFET的漏极电流近似于方波,其占空比等于n×Vout / Vin,最大输出电流幅值则乘以1/n。为滤除输入纹波,必须保证输入电容的ESR很低,具体值根据最大RMS电流来确定。这个RMS电流为

在最小8V电池电压条件下,当最大占空比Dmax为0.144时,从式(5)可以得出Icrms等于9.05A。

电容器制造商给出的电流额定值可能是根据2,000小时的使用寿命给出的,因此必须使用额定值高于采用计算出的Icrms时的电容值。

输入电容值由可接受的纹波量来决定。电容的ESR和AC电流必须很低以满足系统要求。

对快速负载变化的响应

控制器必须对最大的负载阶跃和负载释放进行有效响应。每相导通延迟过程非常长的老式架构的响应速度还不够快,控制器、驱动器和MOSFET也必须有足够快的响应速度,以便满足实时VVID变化的要求。

较早的单边沿设计是等到下一个时钟循环才对控制器在非工作状态下发生的负载瞬态做出响应。它们一次只能对一相提供时钟驱动,从而迫使电源从大电容获得电流。

更新的控制器则通过异步校正来减少负载阶跃响应时间,并同时减少电容器的数量。它们可以立刻导通所有的相来为CPU提供电流,而不会导致内部时钟的延迟。