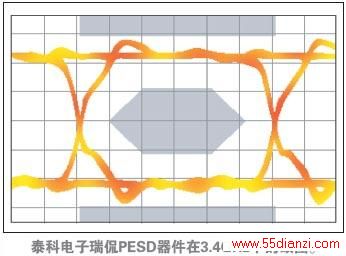

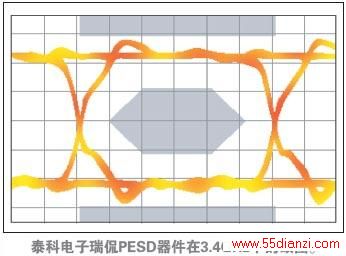

图5.泰科电子瑞侃PESD器件在3.4GHz下的眼图。

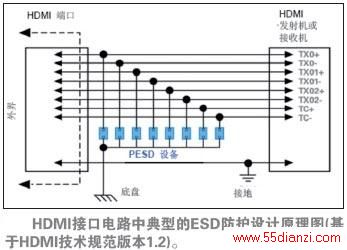

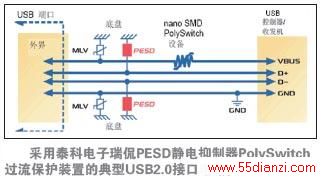

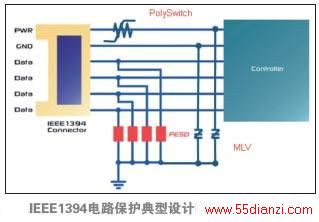

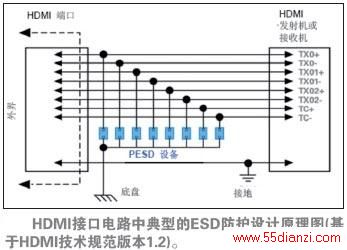

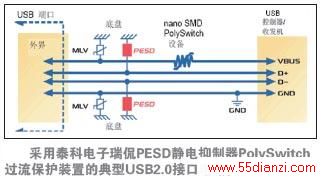

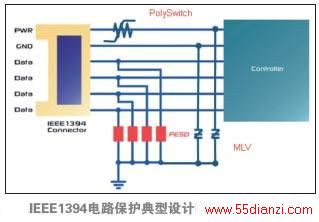

图6、图7和图8展示了利用电路保护部门PESD器件对HDMI1.3、USB2.0和IEEE1394接口电路进行保护的典型应用。这些保护将ESD与敏感电路隔离。在传输线路脉冲(TLP)测试和IEC61000-4-2测试中,尤其是经过多次采样(1000次TLP测试)后,其性能要比其他可比较的元件好。

相对于其他典型的聚合物ESD防护器件,这类PESD器件的较低触发电压(通常150V)和低箝位电压(通常25V)能更好的帮助保护敏感电子元件。该器件采用电子工业中最流行的0603和0402贴装形式,符合RoHS的严格要求;帮助机顶盒敏感电路、手提电脑、手机和其它便携式设备免ESD侵害。

图6.HDMI接口电路中典型的ESD防护设计原理图(基于HDMI技术规范版本1.2)。

图7.采用泰科电子瑞侃PESD静电抑制器和PolySwitch过流保护装置的典型USB2.0接口电路。

图8.IEEE1394电路保护典型设计图。

当选择了一个抑制和电特性(漏电流、电容)与电路参数相吻合的ESD抑制器之后(如PESD),还需要作出另一项选择:抑制器应安装在电路板的什么位置上才能优化电路的ESD保护?“优化”ESD保护指的是使受保护芯片上的ESD瞬变尽可能少。简单地讲,应把ESD抑制器直接放置在连接器的后面。它应该是第一个遭遇ESD瞬变的板级元件。

然后,在实际可行的情况下,任何需要保护的芯片均应尽可能地远离ESD抑制器。采取这一方法将极大地减轻集成电路所承受的应力。下面列出的是PESD器件安装位置的相对优先级,按从高到低的顺序排列如下:

- 设置于作为系统屏蔽(机壳)中的入口的连接器的内部

- 安放于电路板迹线与连接器插脚相互作用的位置

- 放置于电路板上紧挨在连接器后面的位置

- 位于可以高效耦合至I/O线路的性能稳定且未受保护的传输线路

- 设置于数据传输线路上的一个串联阻性元件之前

- 位于数据传输线路上的一个分支点之前

- 靠近IC和/或ASI

另一个需要考虑的布局问题是从PESD到被保护IC的距离和耦合电阻的选择。目标是将该距离降至最小。需要保护的IC通常自身带有ESD保护。但这只属于器件级的防护,且一致性较差,需要PESD器件协助/耦合达到设备/系统级的ESD防护。随着与传输线路之间距离的增加,ESD抑制器变得越发与受其保护的信号线“隔离”开来。

与电路板走线相关联的电感以及任何的封装寄生电感都将在保护电路中加入阻抗,成为PESD电压抑制器和IC间的耦合阻抗。因为IC芯片将要承受抑制器两端和耦合阻抗两端的电压之和,理想的设计应使PESD尽可能多承受应力,同时保证两级防护间没有遗漏的“死角”。

机壳(框架)的地应是ESD基准,而不是信号(数字)地。目的是把ESD从信号环境中屏蔽出去。使ESDTVS保护器件以机壳的地为基准,可免受不希望的噪声效应(如接地反跳)的影响。目标是尽量保持“干净”的信号(数据)环境。

本文关键字:暂无联系方式电子技术,电工技术 - 电子技术