博通BM8750双路10GbE SFI到XFI PHY解决方

博通BM8750双路10GbE SFI到XFI PHY解决方

点击数:7100 次 录入时间:03-04 11:46:23 整理:http://www.55dianzi.com 电子技术

博通(Broadcom)公司的BCM8750是双路10GbE SFI到XFI的 PHY,集成了电散射补偿(EDC)均衡器,支持SFP+线路卡应用. BCM8750是多速率PHY,采用全DSP高速前端,为线路卡设计提供了最高性能和最大的灵活性.片上微控制器实现了对DSP核的控制算法,片上的AGC具有宽动态范围,支持SFP+SR和LR光纤接口.本文介绍了BCM8750的主要特性,主要优势和方框图以及应用框图.

BCM8750 Dual-channel 10-GbE SFI-to-XFI PHY with EDC

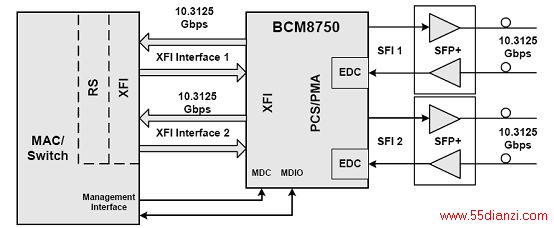

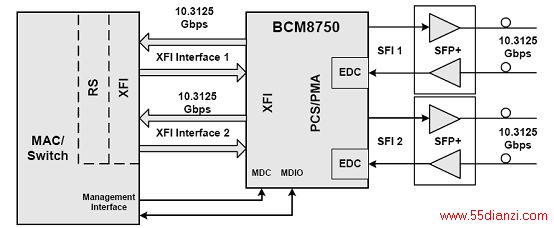

The BCM8750 is a dual-channel 10-GbE SFI-to-XFI (10-Gigabit serial electrical interface) PHY that incorporates an Electronic Dispersion Compensation (EDC) equalizer supporting SFP+ line-card applications.

The BCM8750 is a multirate PHY targeted for optical fiber and copper twin-ax applications. It interfaces with both limiting- and linear-based SFP+ and SFP modules, and SFP+ copper twin-ax cable. The BCM8750 is fully compliant with the 10-GbE SFP+ standard and also supports 1000BASE-X for 1 GbE operation.

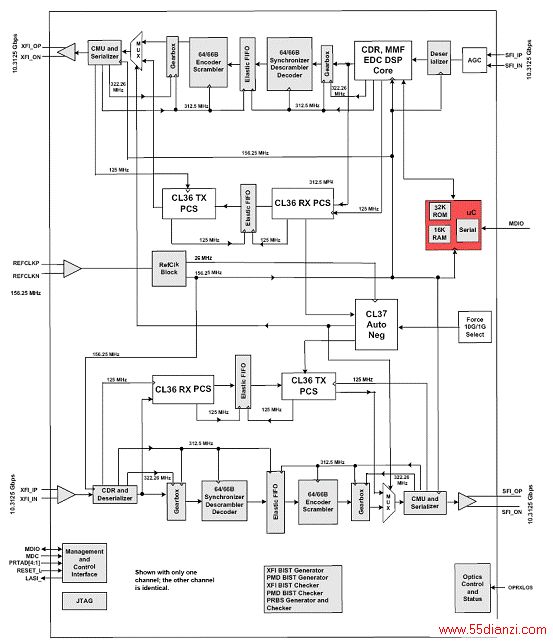

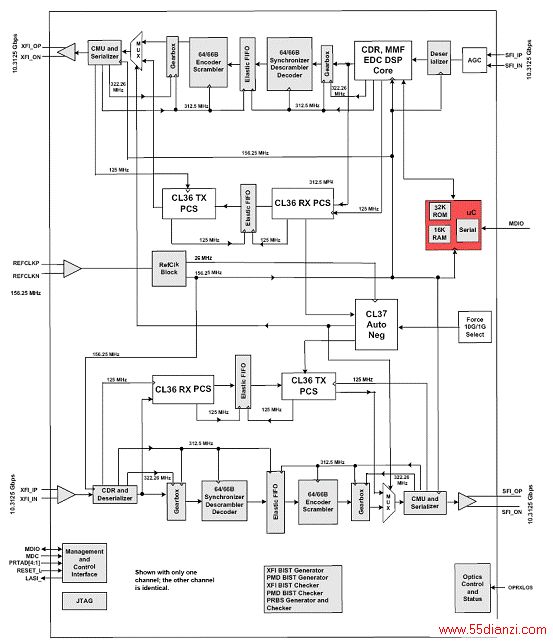

The BCM8750 is developed using an all-DSP high-speed front end, providing the highest performance and most flexibility for line-card designers. An on-chip microcontroller implements the control algorithm for the DSP core.

The BCM8750 is a dual-channel 10-GbE SFI-to-XFI (10-Gigabit serial electrical interface) PHY that incorporates an Electronic Dispersion Compensation (EDC) equalizer supporting SFP+ line-card applications. The BCM8750 is a multirate PHY targeted for optical fiber and copper twin-ax applications. It interfaces with both limiting- and linear-based SFP+ and SFP modules, and SFP+ copper twin-ax cable. The BCM8750 is fully compliant with the 10-GbE SFP+ standard and also supports 1000BASE-X for 1 GbE operation. The BCM8750 is developed using an all-DSP high-speed front end, providing the highest performance and most flexibility for line-card designers. An on-chip microcontroller implements the control algorithm for the DSP core. On-chip clock synthesis is performed by the high-frequency, low-jitter, Phase-Locked Loops (PLLs). Individual clock recovery is performed on the device by synchronizing directly to the respective incoming data streams. A single 156.25 MHz reference clock input is required to the device. The BCM8750 Ethernet PHY is a fully integrated 10-Gigabit serial Ethernet retimer interface. The SFI, XFI, PCS, and PMA functions include 64B/66B coding, Clock Multiplication Unit (CMU), and Clock and Data Recovery (CDR). The BCM8750 is available in a 12 mm x 12 mm, 1 mm pitch, 121-pin BGA, RoHS-compliant package.

BCM8750主要特性:

Dual-channel SFI-to-XFI Physical Layer (PHY) developed in low-power 65 nm CMOS process technology

Integrated microcontroller and AGC with a wide dynamic range

Supports SFP+ SR, and LR optical interfaces

Programmable amplitude control on 10G serial transmitter interface

MDIO interface-compliant with IEEE 802.3ae Clause 45 with extended indirect address register access

Support for XFP/XFI interfaces

SFI and XFI interface: Serial 10.3125 Gbps CML

PCS 64B/66B scrambler/descrambler

SFI receive equalization

Loopback modes supporting IEEE standard modes

Built-In Self-Test (BIST) on SFI and XFI serial interfaces

Low-power dissipation: 1W/10-GbE port

Core supply―1.0V, I/O―3.3V

12 mm x 12 mm BGA package, 1-mm ball pitch

BCM8750主要优势:

Single-reference clock input, enables use of a low-cost 156.25 MHz oscillator

Supports SFP+ copper twin-ax cable

1-GbE mode, with support for IEEE 802.3™ Clause 37 AN

Transmit preemphasis for flexible placement of (PHY)

Link Alarm Status Interrupt (LASI) output for both channels

Advanced diagnostics on SFP+ interface, including eye-mapping, SNR, and BER

BCM8750应用:

High-density 10-GbE SFP+ line cards

SFP+ optical SR, LR, and LRM modules

SFP+ copper twin-ax

图1.BCM8750方框图

图2. BCM8750应用框图

本文关键字:暂无联系方式电子技术,电工技术 - 电子技术