便。可以预见Flash Memory的进一步完善,有可能取代计算机的硬盘,以及更新和诞生许多新的电子产品。[3-3]

ROM的结构和工作原理

24.1.2.1 ROM的结构

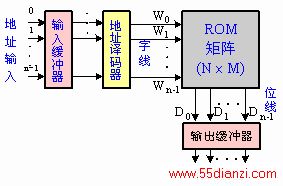

ROM的电路结构主要包括三部分:地址译码器,存储矩阵,输出缓冲器。如图24-1-2所示。

图 24-1-2 ROM的结构图

图中地址译码器有n个输入,它的输出W0、W1、……、Wn-1共有N=2n个,称为字线(或称选择线)。字线是ROM矩阵的输入,ROM矩阵有M条输出线,称为位线。字线与位线的交点,即是ROM矩阵的存储单元,存储单元代表了ROM矩阵的容量,所以ROM矩阵的容量等于W×D。输出缓冲器的作用有两个,一是能提高存储器的带负载能力,二是实现对输出状态的三态控制,以便与系统的总线联接。

24.1.2.2 ROM的工作原理

图24-1-3是一个说明ROM结构和工作原理的电路,ROM矩阵的存储单元是由N沟道增强型MOS管构成的,MOS管采用了简化画法。它具有2位地址输入码,即4条字线W0、W1、W2、W3,有4位数据输出,即4条位线D0、D1、D2、D3,共16个存储单元。地址译码器相当最小项译码器,其输入A1、A0称为地址线。二位地址代码A1A0能给出4个不同的地址。每输入一个地址,地址译码器的字线输出W0~W3中将有一根线为高电平,其余为低电平。即

![]()

![]()

![]()

![]()

当字线W0~W3某根线上给出高电平信号时,都会在位线D3~D0四根线上输出一个4位二进制代码。输出端的缓冲器不但可以提高带负载能力,还可以将输出的高、低电平变换为标准的逻辑电平。如果作为输出缓冲器的反相器是三态门,还可以通过使能端![]() 实现对输出的三态控制。

实现对输出的三态控制。

(a) ROM存储矩阵 (b) ROM矩阵中一条字线的分解图

(a) ROM存储矩阵 (b) ROM矩阵中一条字线的分解图

图24-1-3 MOS 管ROM矩阵字线和位线关系

图24-1-3中4×4=16个存储单元,即跨接在字线和位线上的MOS管,MOS管的栅极接字线,源极接地。MOS管是否存储信息用栅极是否与字线相连接来表示,如果MOS管存储信息,该MOS管的栅极与字线连接,该单元是存“1”;如果该MOS管不存储信息,则栅极与字线断开,该单元是存“0”。根据图24-1-2,例如,当输入一个地址码[A1A0]=00时,字线W0被选中(高电平),其他为低电平,则该字线上信息就从相应的位线上读出,[D3D2D1D0]=0101。ROM全部4个地址内的存储内容见表24-1中。

当给定地址代码后,经译码器译成W0~W3中某一字线上的高电平,使接在这根字线上的MOS管导通,并使与这些MOS管漏极相连的位线为低电平,经输出缓冲器反相后,在数据输出端得到高电平,输出为1。将图24-1-3(a)中与位线D0相连的各字线的有关部分画在图24-1-2(b)中,显然

当给定地址代码后,经译码器译成W0~W3中某一字线上的高电平,使接在这根字线上的MOS管导通,并使与这些MOS管漏极相连的位线为低电平,经输出缓冲器反相后,在数据输出端得到高电平,输出为1。将图24-1-3(a)中与位线D0相连的各字线的有关部分画在图24-1-2(b)中,显然

D

D

D

D

每一个逻辑式是一个或门,即位线与字线间的逻辑关系是或逻辑关系,位线与地址码A1、A2之间是与或逻辑关系。最小项译码器相当一个与矩阵,ROM矩阵相当或矩阵,整个存储器ROM是一个与或矩阵。

ROM存储器的两个矩阵一般与矩阵是不可编的,而或矩阵是可编的。编程时一般要通过专门的编程器,采用一定的编程工具软件进行,以决定存储单元的MOS管是否接入。不过存储单元上使用的MOS管是一种特殊的MOS管,将在下面介绍。

24.1.2.3 集成只读存储器

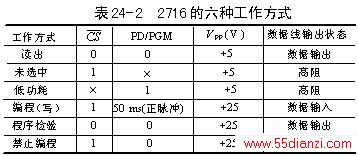

在集成只读存储器中,最常用的是EPROM,EPROM有2716、2732、2764、27158等型号。存储容量分别为2k×8、4k×8、8k×8、16k×8个单元,(型号27后面的数字即为以千计的存储容量)。下面以EPROM2716为例说明它的六种工作方式,见表24-2。它管脚引线如图24-1-4所示,共有24个管脚,除电源(VCC)和地(GND)外,A10~A0为地址译码器输入端,数据输出端有8位,既它有211条字线,8条位线,存储容量为211×8。![]() 是

是

![]() 为低电平起作用片选端,

为低电平起作用片选端,![]() 等于高电平时2716为高阻,与总线脱离,芯片不工作。PD/PGM为低功耗与编程信号,其作用是在两次读出的等待时间内降低器件的功率损耗,既当PD/PGM为“1”时,输出为高阻。在编程时需要在PD/PGM端加编程脉冲,同时要在电源端加较高的编程电压。

等于高电平时2716为高阻,与总线脱离,芯片不工作。PD/PGM为低功耗与编程信号,其作用是在两次读出的等待时间内降低器件的功率损耗,既当PD/PGM为“1”时,输出为高阻。在编程时需要在PD/PGM端加编程脉冲,同时要在电源端加较高的编程电压。

EPROM擦除需专用设备,写入时需要较高的电压,更改存储的数据不太方便。而E2PROM在写数据时不需要升压,用电擦除所需时间也很短(几十毫秒),型号如2815/2816和58064等。

图24-1-4 EPROM2716管脚图

24.1.3 ROM的应用

24.1.3.1 构成组合数字电路

在24.1.2的分析中我们知道,位线与相连的各字线的关系为或逻辑,而字线为地址译码器的输出,地址译码器也叫最小项译码器,所以W实际上是一个与项,从地址输入看,D是一个最小项的与或式。在组合数字电路中我们知道任何一个组合数字电路都可以变换为若干个最小项之和的形式,因此都可以用ROM实现。

例如: 用ROM 构成全加器。全加器的逻辑式为:

![]()

![]()

它有三个输入变量,加数A和B以及低位的进位信号C0,所以选用一个ROM,确定三个地址线,分别代表A、B和C0。从输出位线中选二个,分别代表Si和Ci。于是可以确定或矩阵中的存储单元,为了简单起见,不画出MOS管,接通的MOS管用小黑点表示,如图24-1-5所示,这个简化图称为阵列图。

图24-1-5 用ROM构成全加器的阵列图

所以,用ROM构成组合数字电路的方法是先将逻辑函数化为最小项和的形式,即与或标准型,然后画阵列图。由上述分析可以知道用ROM构成组合数字电路时,不必象用逻辑门构成组合数字电路那样,应先进行划简。因为ROM中给出了全部最小项,用也存在,不用也存在。其次,ROM一般都有多条位线,所以可以方便地构成比较复杂的多输出组合数字电路。

24.1.3.2 序列脉冲发生电路

在各种数字电路中,例如雷达、数字通讯、遥控、遥测等系统中,往往需要一组或多组序列信号,我们可以通过译码器或计数器来实现,也可以用一个N进制计数器加上ROM来实现。序列脉冲有几位,计数器就选几进制的。例如要产生11000100这一序列脉冲,因为它有八位,所以选一个八进制计数器,电路波形图见图24-1-6所示。

ROM除了在单片机和微型计算机中作为存储运行程序外,还有多种用途,分述如下。3=W1+W3图24-1-6 序列脉冲波形图

八进制计数器在CP脉冲作用下,每八个CP脉冲使它的状态循环一次。第一CP脉冲作用之前,总清后,计数器的初始状态为000,m0为“1”,其余最小项为“0”。第一个CP来到后,计数器状态为001,m1=1, 随后m2,…m7依次出现高电平。在位线P1上有关交点打上黑点就可获得11000100序列脉冲输出。该电路可以方便地获得多组序列脉冲的输出。例如P2可输出00111010的序列脉冲。如图24-1-7所示。

图24-1-7 序列脉冲发生器及波形

24.1.3.3 非线性曲线的插补*

在电子电路中经常会遇到器件和电路的非线性问题,例如输出与输入之间有如图24-1-8所示的非线性关系。将该曲线划分为若干段,用若干条折线对曲线进行拟合,划分的段落越多,拟合的越准确。对其中的每一段折线有一个起始点和终点,前一条折线的终点是后一条的起点,根据折线的坐标可以计算出每一折线的斜率。将折线的坐标值和斜率的数字量一一对应存入ROM中,就可以获得一张该电子电路特性的数据表格。

电路工作时,先检测信号是处于哪一个区段,例如x,是处于xi和xi+1之间,于是可以根据下式

计算出该线段的斜率。于是可以计算出对应输入x的输出y值

所以,这是一种线性插补,在保证一

图24-1-8 非线性曲线的拟合

定准确度的前提下,可以减少对曲线的分段数。

本文关键字:存储器 电子技术,电工技术 - 电子技术

上一篇:异步计数器