1 引言

随着科技和经济的发展,嵌入式系统已经被广泛应用到家用市场、工业市场、商业市场、通讯市场和国防市场。PC104是一种嵌入式平台,该平台与IBM的PC机兼容,具有灵活的可扩展性,其小巧的尺寸非常适合嵌入式系统的应用。现代的数据采集要求高速,高精度,需要一个处理能力强的嵌入式平台,PC104正好符合这一要求。

本文基于PCM-3350型PC104嵌入式开发平台,采用MAX1308AD转换芯片,设计了一个16通道,最高采集速度可达1Msps,分辨率为12bit,能够进行通道扫描采集和单通道采集的数据采集系统。

2 数据采集系统设计

数据采集系统主要由放大电路、光耦隔离电路、多路选择开关、带采样保持器的AD模数转换器、时钟电路、CPLD控制电路、数据缓存(FIFO)等部分组成,总结构框图如图1所示:

2.1 A/D转换数据采集电路

A/D转换选用max1308AD芯片,它是一种采样速率最高可达1Msps,分辨率为12bit的采集芯片,多达8个通道的同时采样,+5V模拟电源,+3V至+5V数字电源,其硬件系统连接如图2所示:

2.2 FIFO存储电路

FIFO电路芯片选用IDT公司的IDT7203,它是一个双端口的存储缓冲芯片,具有2048×9 的存储结构,具有12ns 的高速存取时间,结构简单,便于操作,并具有控制端、标志端、扩展端和内部RAM 阵列,内部读、写指针在先进先出的基础上可进行数据的自动写入和读出。

2.3 CPLD控制电路设计

CPLD(EPM7160STC100-6)的设计是本采集系统的核心,它能够对PC104地址总线进行译码,所产生的逻辑控制信号对各个单元的工作状态起控制作用。

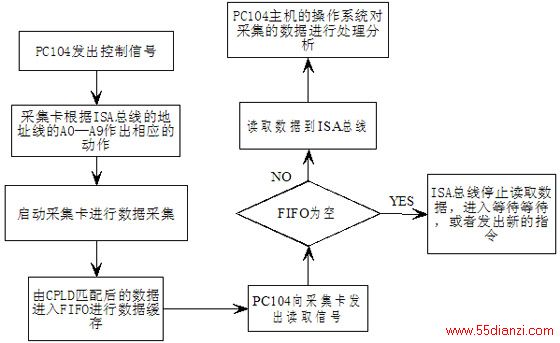

数据的读取可以采用查询的方式。当FIFO的空标号有效时,就产生一个中断,使主机停止对FIFO的读取。在PC104 ISA部分,用到ISA的16位数据总线D[0..15]。A[0..9]是PC104的地址总线;IOW和IOR是对指定设备的读写信号;AEN是允许DMA控制地址总线、数据总线及读写命令线进行DMA传输及对存储器和IO设备的读写。系统工作流程如图3所示:

本文关键字:数据采集 电工基础,电工技术 - 电工基础