module mux_vlg_tst();

reg [7:0] ain;

reg [7:0] bin;

reg clk;

reg enable;

reg rst_n;

wire ready;

wire [31:0] yout;

reg[8:0] i,j;

mux i1 (

.ain(ain),

.bin(bin),

.clk(clk),

.enable(enable),

.ready(ready),

.rst_n(rst_n),

.yout(yout)

);

initial begin

$display("mux example simulation is running.n");

rst_n = 0;

clk = 0;

enable = 0;

ain = 8'Hzz;

bin = 8'hzz;

#1000;

@(posedge clk);

rst_n = 1;

for(i=0;i<256;i=i+1) begin (1)

for(j=0;j<256;j=j+1) begin (2)

mux_ab(i,j); (3)

end

end

$display("mux example simulation is over.All right.n"); (4)

$stop;

end

always #10 clk = ~clk;

task mux_ab; (5)

input[7:0] a;

input[7:0] b;

begin

@(posedge clk); #3;

ain = a;

bin = b;

enable = 1; (6)

@(posedge ready); (7)

@(posedge clk); #3;

if(a*b == yout) $display("%3d * %3d = %5d, it is right.",a,b,yout);

(8)

else begin (9)

$display("%3d * %3d = %5d, it is wrong.",a,b,yout);

$stop;

end

@(posedge clk); #3;

enable = 0; (10)

ain = 8'hzz;

bin = 8'hzz;

end

endtask

endmodule

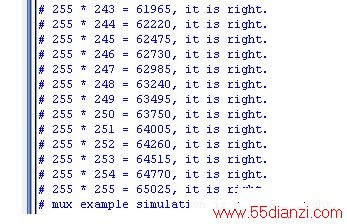

如图2所示,为当前测试结果,我们看到了最后的“mux example simulation is over.All right.”提示信息,表示测试通过。

图2 mux工程测试结果

本文关键字:暂无联系方式电脑-单片机-自动控制,电子学习 - 基础知识 - 电脑-单片机-自动控制