注意,当DACCLK偏移值为00000时,应用SYNC_I延迟(a)与4×线的上升沿之间存在一个DACCLK周期的延迟。

在图6 (b)中,DACCLK偏移值在时间(Z)设为00010.因此,8×、4×和2×设为010(与DACCLK偏移位一致)。4×线(DATACLK输出)的下一个上升沿出现在3个DACCLK周期之后。

如果多个DAC在某一时间窗口内接收到SYNC_I脉冲,并且它们全都具有相同的DACCLK偏移值,则其DATACLK信号同步。因此,多个AD9779器件的数据锁存同时发生。

在初始同步期间,2×、4×和8×计数器位可能不连续。这就是说,在初始应用SYNC_I上升沿时,计数器可能处于这样一种状态,使得同步可能导致其改变多个值。然而,在初始同步完成后,只要SYNC_I的速度保持DATACLK/2或更慢,那么同步脉冲只会在2×、4×和8×位复位到0时出现。(这似乎是多余的,但在实现同步后,SYNC_I脉冲实际上不必应用。)初始脉冲后的周期性SYNC_I脉冲主要用于AD9779器件失去同步这一罕有场合。电源毛刺或不良时钟脉冲触发系统中的某些但不是全部AD9779器件时,可能发生器件失去同步的情况。

时序规格。

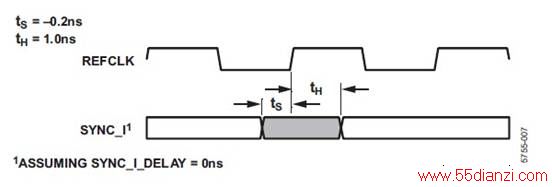

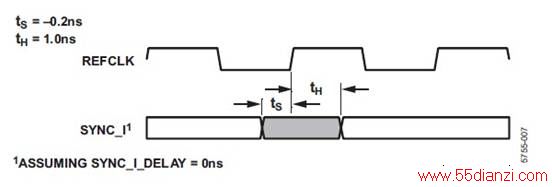

第一个需要注意的时序规格是SYNC_I与REFCLK之间的关系,如图7所示。从AD9779数据手册可知,所需的时序规格为:tS = -0.2 ns,tH = 1.0 ns.

图7. REFCLK与SYNC_I的时序关系

如果DACCLK OFFSET值被设置为非0值,则图7所示的DACCLK信号会左移一个DACCLK周期。同样,如果SYNC_I_DELAY被设置为非0值,则SYNC_I_DELAY每递增一次,图7中的SYNC_I信号就会左移AD9779数据手册给定的SYNC_I_DELAY增量。

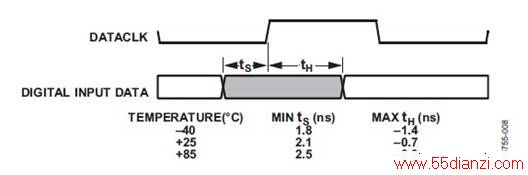

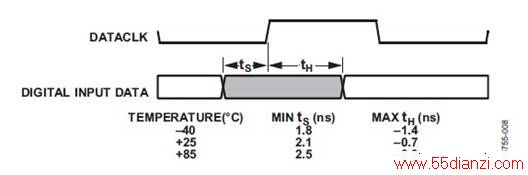

第二个重要时序规格是DATACLK输出与数字输入数据之间的时序关系,该时序信息如图8所示。当DATACLK_DELAY_ENABLE复位时,这些值有效。如果DATACLK_DELAY_ENABLE置1,则DATACLK发生延迟(移至图8右侧),而数字输入数据的采样点保持静止。因此,tS和tH的阻挡窗口相对于DATACLK左移。DATACLK_DELAY_ENABLE置1时,每递增一次的平均延迟和DATACLK_DELAY的增量值参见AD9779数据手册。

图8. 建立保持、DATACLK到输入数据

建立保持数据与REFCLK的关系参见AD9779数据手册,某些应用中该数据也是必要的。

上一页 [1] [2]

本文关键字:暂无联系方式变换电路,单元电路 - 变换电路