⑤16行扫描显示方式下,一个大型LED屏分为16行同名行,每一同名行按照①、②、③、④原则进行点阵排序。

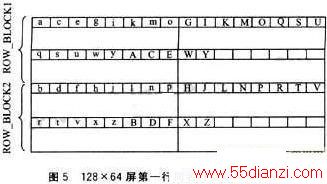

以一个128×64的点阵屏第一行同名行的数据排序为例,如图5所示,第一行同名行的点阵码的存放顺序应依次为:a,b……z,A,B,……z……。

使用并行总线DMA数据传输技术简化了LED显示系统的软硬件设计,降低了系统成本,取得了很好的显示质量,在22.1184MHz的系统时钟下,512×256(8m2)单色点阵屏显示帧频达到250Hz,平均120ns传送1个字节,达到了使用单CPU系统代替多机系统控制LED显示系统的目的。但为了使上一代的显示驱动板仍能够使用,点阵码需要排序,显示时只能使用页面方式显示,这样在多页动态滚屏显示时需要大容量的存储器。对于512×256单色点阵屏需要数十兆的容量,使用32位ARM7TDMl内核先进控制器S3C44BOX和廉价的大容量SDRAM存储器可以使该问题得到很好的解决。若使用针对DMA控制显示设计的显示驱动板显示时,点阵码就不需要排序,一片数百KB的SRAM就能满足系统要求了。

本文关键字:暂无联系方式显示电路-显示屏,单元电路 - 显示电路-显示屏