摘要:详细描述了一种内置于AM-OLED显示驱动芯片中的单端口SRAM电路的设计方法,提出了一种解决SRAM访问时序冲突问题的仲裁算法。同时给出了基于0.18μm标准CMOS工艺设计的一款大小为320x240x18位的SRAM电路。通过HspICe仿真结果表明,该结构的动态功耗相对于传统结构可减小22.8%。

关键词:低功耗位线结构;单端口;静态随机存取器;仲裁器;显示驱动芯片

0 引言

近年来,OLED(有机发光二极管)的低功耗、主动发光和超薄等优势已具有逐步取代LCD(发光二极管)的趋势,被认为是未来20年成长最快的新型显示技术。将SRAM、电源电路、源驱动电路、时序控制和接口逻辑等功能模块集成在一块的AM-OLED (有源驱动有机发光二极管)显示驱动芯片是手机OLED屏和MCU(微控制器)之间的接口驱动电路。而其内置SRAM是整个芯片中一个非常重要的模块,可用于存储一帧图像的数据。但由于它占据整个芯片大部分的硅面积,因此,它对芯片整个的面积有着决定性的影响。

SRAM功耗在整个芯片中占据很大比重。近年来,对低功耗SRAM的研究很多,其中降低动态功耗主要依靠降低寄生电容和限制位线电压摆幅。事实上,在驱动芯片对SRAM速度要求不高的情况下,以牺牲读取速度来换取SRAM的功耗和面积是可行的。而另一方面,SRAM又存在访问时序冲突问题,其传统方法是采用双端口SRAM结构来实现同时读写功能,但这样会大大增加内置SRAM的面积。为此,本文采用时分技术来使单端口SRAM具有双端口结构的功能,并采用仲裁电路来划分两种请求信号的优先权,以将外部两个并行操作信号转化为内部单端口SRAM的顺序执行,从而使两种请求信号完全处于独立的时间操作域内。

1 SRAM电路的传统结构

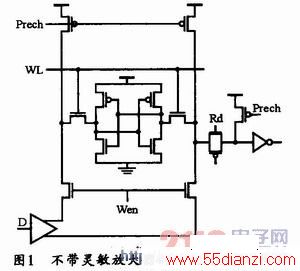

图1所示是传统六管SRAM的电路结构,它主要包括存储单元、预充电路、写入驱动和输出电路。由于是单边输出,因而无需灵敏放大器和平衡管。

当图1电路在读出数据时,预充信号Prech变低,以把两边位线电位拉到高电平,字线WL变高,其中一条位线通过存储单元放电到低电平,使读出电路导通,将位线信号读出锁存。而在写入数据时,预充电路也会先对两条位线充电到高电平,以便读信号Wen开启两个NMOS管,写驱动电路将其中一条位线电位拉到低电平,然后字线打开,将数据写入存储单元。由于在读写过程中,预充电路每次都要对两条位线进行预充电,故会造成功耗的浪费。经过对该电路的具体分析,本文研究并提出了一种低功耗的位线结构。

www.55dianzi.com

2 SRAM电路的低功耗设计

嵌入式SRAM的功耗大致分为动态功耗和静态功耗。对应到SRAM的具体模块上,其功耗主要消耗在译码器、字线驱动、位线预充、灵敏放大器以及静态漏电流上。译码器可以用与非门逻辑来代替伪NMOS逻辑设计以降低功耗,由于本电路结构没有灵敏放大器电路,因而无需考虑其功耗。下面主要就动态功耗进行优化。

SRAM电路的动态功耗计算公式如下:

![]()

式中,iactive为工作单元的等效电流;ileak为不工作单元的漏电流;CDE为每个译码器的输出节点电容;VINT为内部电源电压;iDC为读操作消耗的直流电流;△t为直流电流的激活时间;CPT为CMOS逻辑电路和外围电路的总电容;IDCP为外围电路的静态电流。本文分别从降低位线寄生电容及其电压摆幅来降低SRAM的整体功耗。

2.1 降低寄生电容

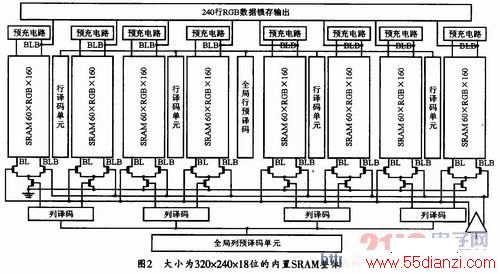

降低寄生电容可采用位线划分技术(DBL)和字线划分技术(DWL),即将位线和字线划分成多级,以降低位线寄生电容和字线寄生电容,这样即可降低读写功耗,也能提高数据的读写速度,进一步提高SRAM的整体性能。图2所示是一个大小为320x240x18位的SRAM存储阵列的整体结构。该结构将240x18列分成4块,每块包含60x18位数据;320行则分成左右两级,每级含160行。这样就把整个阵列分成了8个小模块,每块大小为160x60x18位,这样就使得字线电容降到了原来的1/4。位线电容则降为原来的1/2。

2.2 降低位线电压摆幅

由于传统结构中,整个读写过程的预充电路都会对两条位线进行预充电,故会造成功耗的浪费。而读电路是采用单边输出,位线上的电压摆幅则必须采用全摆幅形式,因此,只能通过降低写操作时的电压摆幅来降低功耗。

www.55dianzi.com

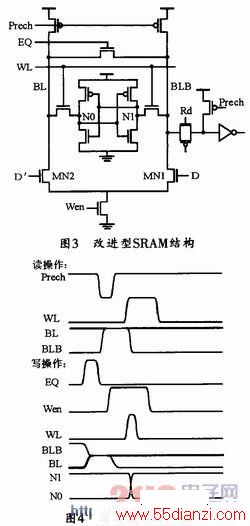

图3所示是采用低功耗位线技术的改进型SRAM的结构图。该电路结合单端输出来得到SRAM的电路结构。该电路与传统电路的两个不同之处:一是写驱动电路采用单边驱动结构,且增加了一个平衡管来防止数据丢失。而在写操作时,只需对一边位线下拉到低电平来写入数据,另一边位线浮空;二是预充电路只在读操作时充电,在写操作时不充电。

图4所示是新SRAM结构电路的工作时序图。该电路在读操作时,Prech变低,预充电路位线充电到高电平,字线变高,位线BLB通过存储管放电到低电位,读取电路读BLB上电压信号,数据读出;而在写操作时,先平衡位线电位,以防止数据丢失。假设原来存储管里存储的是“0”,要向其中写入数据“1”,则写使能信号Wen先从低电平变到高电平,此时D为高电平,D’为低电平,MN1管导通,MN2截止,位线BL悬空,位线BLB被拉到低电平,字线变高,传输管导通,以便向存储管里写入数据“1”。

在字线变高时,同字线上的其它单元的位线BL、BLB会通过存储管里的上拉PMOS管和下拉NMOS管充放电到一定电位。为了防止在写操作时位线充放电过多而导致浪费,可减小字线选择信号的脉宽,以缩短对位线的充电时间。

3 仲裁器模块设计

仲裁器电路分为仲裁和时序产生等两部分,其中仲裁部分处理MCU送来的读写请求和显示控制器送来的读请求信号,并判断它们的优先级别,然后把请求信号送入时序产生电路。时序产生电路负责产生sram模块的控制信号。

3.1 仲裁器电路

仲裁器模块主要用来处理行扫描以及MCU读写产生的时序冲突问题,也就是在这两个信号同时送过来时,先判断它们的优先级,同时将外部两个并行操作信号转化为内部单端口SRAM的顺序执行,从而使两种请求信号处于完全独立的时间操作域内,以减小内置SRAM的面积。鉴于MCU读写速度大于显示行扫描速度,MCU读写信号的优先级别应高于显示读信号。

www.55dianzi.com

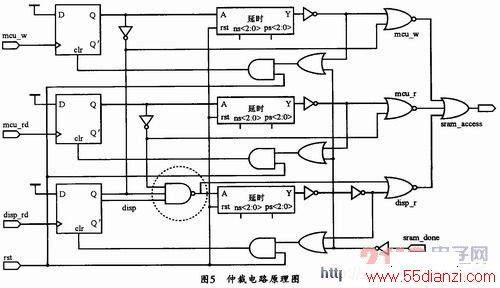

图5所示是仲裁器的具体实现原理图,图中有三个请求信号,其中MCU的读写请求信号(mcu_wr、mcu_rd)以及显示数据输出信号(disp_ rd)两类请求信号对外部是相互独立的,但MCU读写请求信号在内部不是相互独立的,一个MCU读写周期只对应一次读或写操作。其优先级的判断主要是通过图5中的与非门来实现的。下面通过两种时序冲突来说明优先级判断方法。

www.55dianzi.com

仲裁器首先接受来自显示控制模块的SRAM读操作请求,然后接收来自MCU的写请求。这时,mcu_wr有一个上升沿,D触发器将锁存输出高电平,并经反相器反向输送到与非门,与非门输出低电平,使disp_r置“0”,以打断显示读信号响应,直到仲裁器处理完sram_wr信号请求,再由时序产生电路反馈一个完成信号sram_done,并清零sram_wr的D触发电路。由于显示读的D触发器的输出信号disp保持高电平,使与非门的输出变高,disp_r重新置为“1”,同时重新处理打断的disp_rd信号。

第二种时序冲突是仲裁器先收到外部MCU的读请求信号,在还没有结束处理这个请求信号时,显示控制模块的并行读请求信号已送到仲裁器。这时请求信号disp_rd的一个上升沿使disp由低电平变为高电平,此时mcu_rd的D触发器输出保持为高电平,与非门不受disp信号的影响,一直输出高电平。由于显示读请求信号被延迟,直到处理完MCU读请求信号,清零信号开启,使mcu_rd的D触发器输出低电平,这时,与非门输出高电平,disp_r重新置为“1”,时序产生电路响应其请求。

3.2 时序产生电路

由仲裁器电路产生的总请求信号sram_aCCess送到这里后,可用以产生SRAM时序控制信号。该模块采用单稳态时序电路结构来实现其功能,其难点主要是解决预充信号Prech和字线选择信号WL的产生问题。根据SRAM的存储结构可知,Prech只在读操作才对位线充电,写操作时不充电;由于字线选择信号WL在读操作和写操作时的脉宽不一样,故需要采用不同时延模块,并根据不同操作,通过传输门来选择输出WL信号。

本文关键字:暂无联系方式显示电路-显示屏,单元电路 - 显示电路-显示屏