在这个系统中,需要考虑的另外一个参数是SRAM的tJIT:相对于数据的SRAM输出源同步时钟抖动。这可能是由管脚间时钟到输出的时间变化而引起的。

在 这个例子中,我们假设时钟和数据走线匹配地很好。如果由于电路设计而导致走线长度出现差异,就必须考虑时钟和数据信号走线长度的差异。如果时钟信号的走线 是有意延长以延迟时钟信号(将时钟信号与数据有效窗口中心对准),就不用考虑此参数。假设SRAM源同步时钟抖动为tJIT=±0.2ns,我们可以像表 中列出的那样逐步计算最小周期时间(参见表)。要获得非负值裕量,应满足如下条件:

tM>0

tCYC/2-2.2ns>0

tCYC/2>2.2ns

tCYC>4.4ns

fCYC<227MHz

本例采用源同步时钟信号,满足建立和保持时间要求,对数据信号走线长度也没有什么约束。计算得到的最大工作频率是277MHz,比传统时钟同步方法提高了35MHz。注意本例中主要的频率限制因素是控制器的建立和保持时间。

使用源同步时钟的最优方法

为最好地利用源同步时钟,设计工程师应注意以下要点:

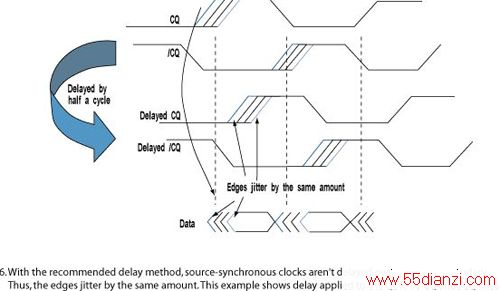

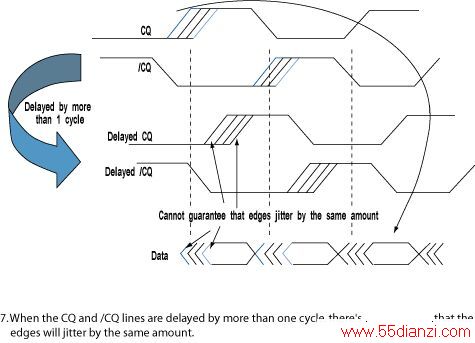

不 要使源同步时钟的延迟时间超过一个周期。源同步时钟的上升沿与其所驱动的数据信号是严格匹配的,所以时钟和数据信号应具有同样的抖动并互相抵消。如果将源 同步时钟信号的上升沿延迟到下一个周期以锁存数据,那么就必须考虑另外一个抖动成分,即N周期抖动,N是相对于数据信号,时钟信号被延迟的周期数。图6和 图7中给出了使用源同步时钟的推荐方法和不推荐方法。这些例子采用QDR-II源同步时钟(CQ和/CQ)。

注意:如果有两个源同步时钟,最好两个都用到。

本文关键字:接口 接口电路,单元电路 - 接口电路