本系统在FPGA芯片EPM570GT100C4的基础上可利用软件QUARTus II来开发逻辑控制功能, 从而实现对W3150A+的控制。其主要端口如下:

nrst: 复位输入键, 低电平有效;

clk : 时钟输入;

nwrst 复位输出, 可复位W3150A + 和

RTL8201;

nwr: 对W3150A+写使能信号, 低电平有效;

nrd: 对W3150A+读使能信号, 低电平有效;

ncs: W3150A+片选信号, 低电平有效;

address: 15位地址信号;

data: 8位数据信号;

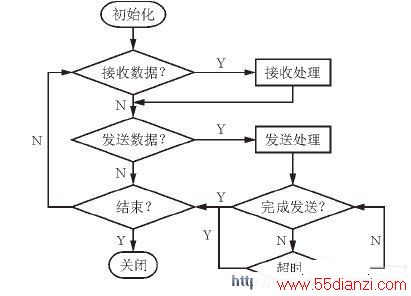

本接口通信设计采用的是UDP通信方式, 其通信流程图如图5所示。

图5 UDP通信流程图。

端口初始化主要是对端口进行初始化, 包括设置UDP模式、设置端口号, 设置 OPEN 命令;通过Sn_RX_RSR寄存器的值可检测是否收到数据, 若非零, 即进入数据接收处理; 接收处理时, 首先读取Sn_RX_RSR寄存器的值, 即接收数据字节数, 然后计算偏址和实际物理地址, 再根据物理地址读取数据。在读取数据过程中, 如果物理地址到达该端口设定的高限地址, 则先读高限地址的数据, 然后将物理地址改为基地址, 然后再从基地址继续读取剩余的数据。读完所有的数据后, 可将Sn_RX_RR的值加上读取的数据长度, 然后写入Sn_RX_BASE, 最后再向端口n的指令寄存器写入RECV命令。

发送数据? /发送处理的实现过程是首先读取S_TX_FSR寄存器的值以便能使用发送数据空间的大小来计算偏址和实际物理地址, 然后再从物理地址写入要发送的数据。在发送数据过程中, 如果物理地址已到达该端口设定的高限地址, 则先将数据写入高限地址, 然后再将物理地址改为基地址, 接着从基地址继续写入数据。写完所有的数据后, 再将Sn_TX_WR的值加上发送的数据长度, 然后写入Sn_TX_BASE, 最后向端口n的指令寄存器写入SEND命令。

发送完成的确定可在发送(SEND) 命令后,通过检测Sn_CR的值来判断数据是否全部发送完成。

当远程对端不存在或数据传输不正常时, 将产生超时错误。此次可以通过对Sn_IR (TIMEOUTbit) 检测来判断是否超时。

当操作全部完成时, 应关闭窗口, 即将Sn_CR寄存器置为 CLOSE 。

4 结束语

本文介绍了以太网接口的设计及其数据传输的实现过程。利用本文的方法可以使以太网接口正常运行, 故可为后续的虚拟仪器开发奠定基础。事实上, 本方法已经过多次试验证明: 完全满足工程需要。

上一篇:取自USB端口的电源电路