随着SOC技术、IP核技术的发展, 锁相环 作为一个基本的ASIC宏单元,它在无线通讯和微处理器电路中作为时钟电路的应用将更加广泛[1]。特别是现代通讯业的迅速发展,蜂窝电话(Cell Phone)和蓝牙技术(Blue Tooth)的涌现,对片内同步和片间同步都提出了新的要求。

本文对锁相环的工作频率、工作速度、相位噪声特性等方面进行考虑,设计了一种适用于 时钟恢复 系统的PLL锁相环路,与以往的电路相比,具有高速、低噪声的特点。

1 PLL简介

PLL锁相环路在时钟恢复系统中实现时钟信号的倍频与分频,生成本地时钟信号,提供给延迟锁相环模块,用于外部通信的时钟恢复[2]。

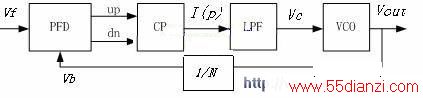

本文设计的PLL锁相环路用于将12MHz的稳定外部晶振低频信号转换为480MHz的高频时钟信号的时钟恢复系统中。整体电路模块的设计方案如图1所示。

图1 电路模块图

基本原理为:鉴频鉴相器检测参考时钟信号Vf与压控振荡器输出信号Vout的相差和频差,产生一个上升(up)或者下降(dn)脉冲信号并送入电荷泵,控制电荷泵[3]给环路滤波器电容充放电。环路滤波器滤掉信号中的高频部分,再将结果送入压控振荡器。压控振荡器根据控制电压的变化改变输出,经过分频器反馈到鉴频鉴相器。如此循环,最终锁定输出Vo。

2 PLL模块设计

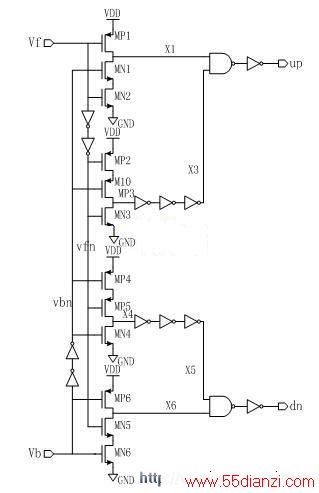

2.1鉴频鉴相器

鉴频鉴相器的设计采用了一种新型biPFD结构,如图2所示。这种新型biPFD双边鉴频鉴相器结构的主要优点是放置在nc-stage和pc- stage之间的两对反相器可以有效地防止π相位死锁。更重要的是,由于pc-stage输出端所接的三个反相器延时单元的作用,在鉴频过程产生大相位误差时,则进行双边鉴频鉴相,若当相位误差减小到一定程度以后,它就自动变为单边鉴相。

这样既保留了双边鉴频鉴相器收敛速度快的优点(因为环路频率锁定时间远大于相位锁定时间),又克服了一般双边鉴频鉴相器在锁定时,要求双边对齐,而导致稳态相差和相位噪声大的缺点。

图2 双边鉴频鉴相器结构

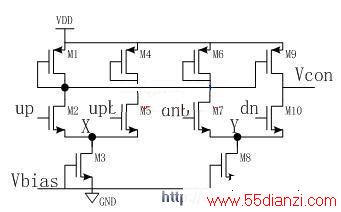

图3 对称负载的电荷泵

图4 偏置电路结构

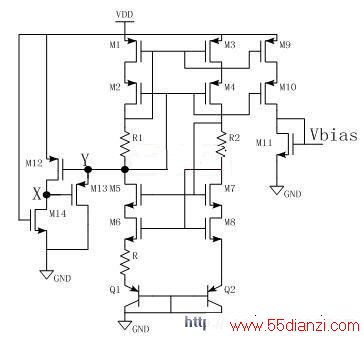

2.2电荷泵

电荷泵结构如图3所示。这种电荷泵由两个NMOS源耦合对组合,各自都有独立的电流源,并与对称负载单元构成的电流镜相连。当up信号有效时,电流将通过电流镜镜像至右侧,对环路滤波器充电;当dn信号有效时,直接通过NMOS管对滤波器放电;而当up和dn信号同时有效时,由电流镜提供的电流将与 NMOS管的电流相互抵消,此时对滤波器充放电电流为零。

在任一时刻,up和upb信号(dn和dnb信号)控制的两个NMOS管中,总有一个是导通的,从而使X节点(Y节点)电压几乎保持不变,并且在 up信号(dn信号)开启或关闭时,也不会发生电流过冲的现象。由于对称负载的电荷泵采用了对称负载单元,具有良好的匹配特性,因此,也不会出现电荷分享现象,其稳态相差比较小。以及电荷泵引起的环路输出信号的抖动将会很小。

另外,电荷泵需要稳定的电流源来保证环路工作的稳定性,因此在设计中,偏置电流通过带隙电流源产生,带隙电流源结构如图4所示。M12、M13、M14构成启动电路,其中M12取较大宽长比,M14取倒宽长比。当电路加电时,M14首先导通,X节点电平迅速下降,使M13导通,此时M1、M2、R1和M13构成一条通路,使带隙电流源有了启动电流。M13导通以后,Y节点电平下降,使M12导通,由于M12宽长比较大,而M14为倒宽长比,所以X节点电平上升,使M13关断。也就是说,M13只在电路加电一瞬间导通,带隙电流源正常工作时,M13一直处于关断状态,对带隙电流源没有任何影响。

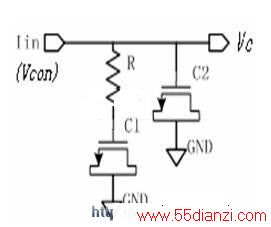

2.3环路滤波器

环路滤波器的设计选择了最常使用的二阶低通滤波器结构,如图5所示,使整个锁相环构成三阶环路。

图5 二阶低通滤波器

图6 反相器型压控振荡器

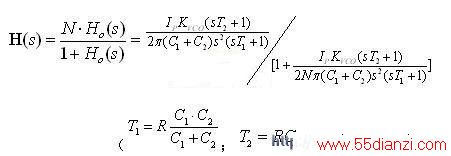

其系统闭环传递函数为:

式中:IP为电荷泵电流,KVCO为压控振荡器增益,N为分频系数,R是滤波器电阻,C1,C2为滤波器电容。

事实上,为了简化对工艺的要求,这里的电容采用MOS管栅电容来实现。

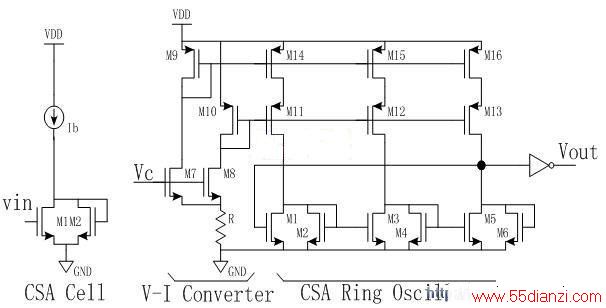

2.4压控振荡器

采用的压控振荡器如图6所示,该结构也称为最小电流模压控振荡器结构,由三级CSA(Current-Steering Amplifier)组成。每个CSA结构包括一个电流源和两个NMOS管(M1、M2),是一个放大电路单元,该结构不仅结构简单,而且输出振荡摆幅也比较大[4]。

其振荡原理如下:当Vin为高电平时,M1管导通,电流源上的电流Ib通过M1管放电,M2管进入截止区,在这种情况下,M1管的导通电阻决定了振荡的最低电压VOL,反之,M1管截止,M2管饱和,其饱和电阻的大小决定了振荡的最高电压VOH,可通过控制电流Ib达到控制振荡频率的目的。

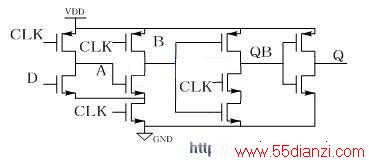

2.5 分频器

在分频器电路上采用了双预充电TSPC D触发器的结构[5],如图7所示。

图7双预充电型TSPC DFF

该结构大大缩短了DFF的建立时间。在预充电阶段(时钟CLK为低电平时),节点A、B预充到高电平,进入锁存状态。对于传统的TSPC D触发器,输入数据就传到节点A,相应的充电时间就比较长。在求值阶段(时钟CLK为高电平时),输入数据直接传到QB。TSPC的建立时间是指输入数据变化和时钟触发沿之间的最小从而采用双预充电TSPC D触发器构成的间隔,可见双预充电TSPC D触发器的建立时间要比传统的TSPC D触发器快得多,分频器速度也会相应的比较快。

分频器电路采用了40级分频器(不包括压控振荡器输出端接的一个二分频器),首先由3个双预充电TSPC D触发器和门电路组成5分频电路,再由3个串联的二分频器组成8分频的电路,因为结构比较简单,在这里不再介绍具体电路。

3电路仿真

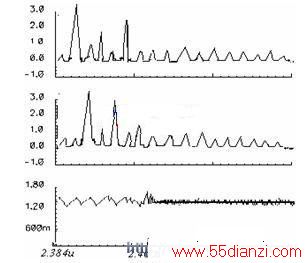

本设计在H SPICE 的平台下采用2.5V,0.25μm First SILicon CMOS工艺仿真。图8为PLL环路锁定过程的波形图,图9显示了PLL输出频率为480MHz信号时的频谱图。从仿真结果可知,频谱呈现出较高的纯度,从而表明环路的相位噪声很小;并且在480Hz时锁定时间仅为2.4us,大大的提高了工作速度,达到了设计的目的。

图8锁定过程的波形图

图9 PLL输出信号频谱

4结论

本文作者创新点:通过对PLL 锁相环 各模块进行设计,根据采用的CMOS工艺特点和要求,设计环路各部件具体的电路形式,最终得到了高速、低噪声的高性能锁相环,适应了当今电子技术的发展趋势。

参考文献

[1] 李肃刚,杨志家.一种改进的全数字锁相环设计[J].微计算机信息,2005,9-1;42-43.

[2] 王福昌,鲁昆生.锁相技术[M].华中科技大学出版社,1997.

[3] 姜梅,刘三清.用于电荷泵锁相环的无源滤波器的设计[J].微电子学,vol.33, No.4, Aug. 2003.

[4] V.R.Von Kaenel. A High-Speed, Low-Power CLOCk Generator for a Microprocessor Application[J]. IEEE Journal of Solid-State Circuits, vol.33, No.11, Nov.1998.

[5] 陈贵灿,程军,张瑞智.模拟CMOS集成电路设计[M].西安交通大学出版社,2003.

本文关键字:锁相环 锁相环电路,单元电路 - 锁相环电路

上一篇:全数字锁相环的设计及分析