根据本系统在Z 域的误差传递函数和实际设计参数,可以分别得到系统在相位阶跃、频率阶跃和频率斜升信号作用下的响应曲线如图4 所示。从图4 中可以看到,系统对于上述信号的稳态跟踪误差均为零。这与理论分析所得出的结论也是一致的。综合考虑锁相系统的稳定性、稳态相差和锁相速度等性能指标, 最终选择设计参数K1 = 2-3 , K2 = 2-6, K3 = 2-11。

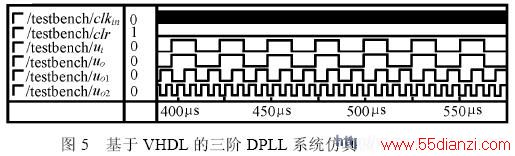

图5 给出了采用EDA 技术设计的三阶全数字锁相环的系统仿真波形,图中clkin 为系统时钟信号,clr 为系统复位信号, ui 为输入信号, uo 为输出信号, uo1 为二倍频输出信号, uo2 为四倍频输出信号。从图5 中可见,本锁相系统可以同时得到倍频输出信号。

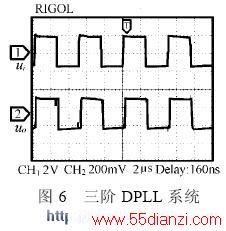

图6 给出了用FPGA 实现的三阶全数字锁相环的硬件电路测试波形。系统仿真与硬件测试结果都表明,该系统能够实现锁相功能。

4 结论

本文提出了一种基于PI 控制算法的三阶全数字锁相环,采用EDA 技术进行系统设计,并用可编程逻辑器件予以实现。该锁相环具有电路结构简单、控制灵活、跟踪精度高、环路性能好、易于集成的特点。在锁相速度和稳定性方面优于已有的采用脉冲序列低通滤波计数方法实现的数字锁相系统。理论分析和仿真实验表明,改变比例积分控制参数,可以很方便地调节锁相系统的锁相速度和稳定性,因而简化了设计过程。硬件测试结果证实,应用EDA 技术设计的 高阶全数字锁相环 能够实现其锁相功能。该锁相环可作为功能模块嵌入SoC 内,为各种控制系统提供快速、稳定和高精度的同步信号。

本文关键字:锁相环 锁相环电路,单元电路 - 锁相环电路