2 ADPLL的结构及工作原理

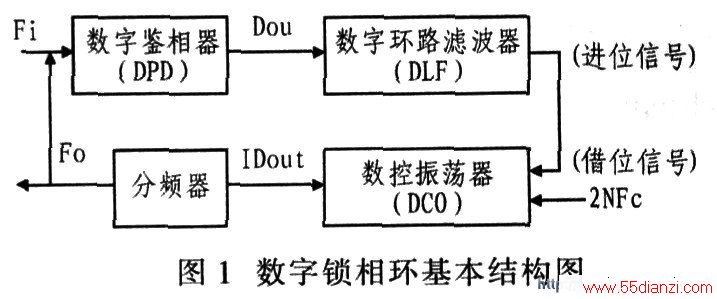

图1给出全数字锁相环(ADPLL)的基本结构。主要由数字鉴相器DPD,数字环路滤波器DLF,数控振荡器DC0,分频器4部分组成,其中心频率为fc。DPLL是一种通过相位反馈来控制系统的电路结构。根据输入信号Fin和本地时钟输出信号Fout之间的相位误差信号送入数字环路滤波器,并对相对误差进行平滑滤波,生成控制信号carry和bor―row,数字振荡器根据控制信号调节反馈,使输出信号Fout的相位逐渐跟踪输入信号Fin的相位,最终达到锁定。

3 ADPLL各模块的功能和具体实现方法

3.1 数字鉴相器

常用的鉴相器有2种类型:异或门(X0R)鉴相器和边沿控制鉴相器(ECPD),设计中采用异或门鉴相器。异或门鉴相器用于比较输入信号Fin和输出信号Fout之间的相位差,并输出误差信号Dout,Dout作为计数的方向信号输入给下一级。

3.2 数字环路滤波器

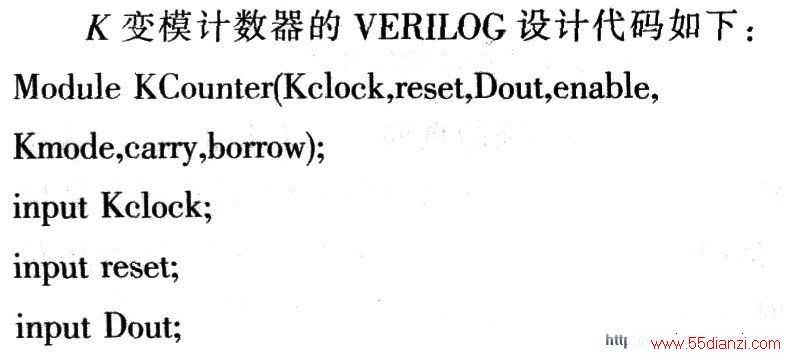

数字环路滤波器(DLF)由一个模值为变量K的可逆计数器来实现。其作用首先用于消除数字鉴相器输出的相位误差信号Dout中的高频分量,保证锁相环路性能的稳定性和准确性:其次K变模计数器再根据鉴相器的相位误差信号Dout来进行加减运算。若Dout是高电平时,计数器进行加运算,直到相加结果达到预设模制K,则环路滤波器输出一个进位脉冲信号carry给数控振荡器;若Dout是低电平时,计数器在模值K的基础上进行减运算,直到为零,并输出一个借位信号borrow给数控振荡器:当环路锁定或只有随机干扰脉冲时,Dout是一个占空比为50%的方波,即计数器的加减数目基本相等,计数结果在K附近上下徘徊,不会产生进位或借位脉冲,大大减少了由随机噪声引起的对锁相环路的误控。也就是说,采用K计数器作为滤波器,有效的滤除了噪声对环路的干扰。

www.55dianzi.com

上述代码经过在QUARTus II上编译仿真后其波形如图2所示。

设计中适当选取K值特别的重要。如果K值偏大,这样计数器对少量噪声干扰不可能计满,就不会有进位或者借位脉冲,有利于抑制随机噪声;但就会使捕捉带减小,导致环路进入锁定的时间变长;如果K值偏小,可使环路尽快进入锁定状态,但会减弱对噪声的抑制能力,导致环路频繁的产生进位或借位脉冲,造成整个系统不稳定,产生相位抖动问题。所以要适当选取K值。

3.3 数控振荡器

数控振荡器采用的是脉冲加减电路。时钟为2NFC。当没有进位/借位信号时,其输出对外部时钟进行二分频;当有进位信号carry输入时,则在原信号中插入半个脉冲,以提高原有信号的频率;当有借位信号borrow输入时,则减去半个脉冲,以降低原有信号的频率。

3.4 可变分频器

可变分频器实际上就是一个除N计数器,是把脉冲加减电路的输出信号再做N分频,通过不断调整N值的大小,使分频器的输出信号能与输入信号的相位保持同步,以达到锁相环的锁定。

由锁相环的整个工作过程可知,全数字锁相环经过一些特定改良后,可在某些情况下作为满足一定频率要求的信号发生器使用。

4 FPGA片内系统结构

为了平衡系统的稳定性和捕获带宽之间的矛盾,就要找到一个最佳的K值,使系统在最大可能消除干扰的前提下,捕捉带达到最大,捕获时间最短,其整个过程由CPU来控制。CPU的选择主要有2种方案:①FPGA片内实现CPU;②与片外系统共用CPU。这里主要介绍第一种。

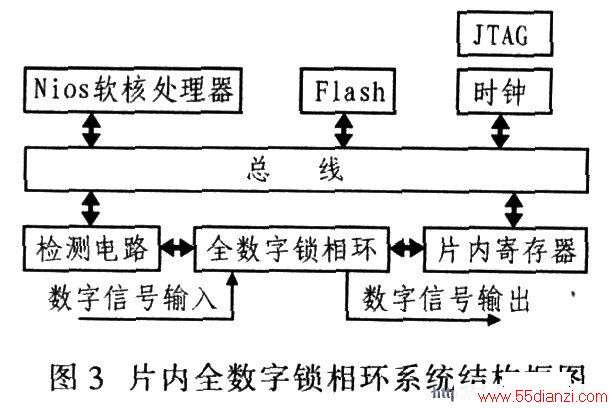

对于片内CPU,这里采用Ahera公司推出的NiosⅡ嵌入式软核处理器予以实现。在系统中,片内寄存器,全数字锁相环以及检测电路均作为外设嵌入到FPGA芯片中。片内寄存器,全数字锁相环,检测电路通过系统总线相连接,受到片内的NiosⅡ软核处理器的控制,使得全数字锁相环中的数字环路滤波器部分在工作中的参数得到优化。此种结构使得NiosⅡ处理器和全数字锁相环2部分集成在一块FPGA器件中,大大提高了系统的稳定性和可靠性。罔3给出片内全数字锁相环系统结构框图。

5 试验仿真结果分析

整个系统经过软硬件调试后,就对该锁相环进行测试和验证,采用Quartus II软件中集成的仿真器进行仿真。图4给出仿真波形。

可见,在有进位/借位信号输出时,波形中自动加入/减去半个脉冲,经过几次调整后系统达到锁定状态。

6 结语

通过在单片FPGA中实现智能全数字锁相环,NiosⅡ嵌入式处理器随时检测锁相环的状态,适时调整锁相环的参数,从而能缩短锁相环锁定时间,提高效率;并逐渐改进其输出频率的抖动特性。解决了锁定时间与相位抖动之间的矛盾,提高了信息的传输效率和质量。全数字锁相环在数字通信,数字信号处理,电力系统自动化等众多领域有着极为广泛的应用,随着片内数字锁相环系统研究的不断深入与发展,其性能会不断提高,其意义重大,前景广阔。

本文关键字:锁相环 锁相环电路,单元电路 - 锁相环电路

上一篇:一种可编程的全数字锁相环路的实现