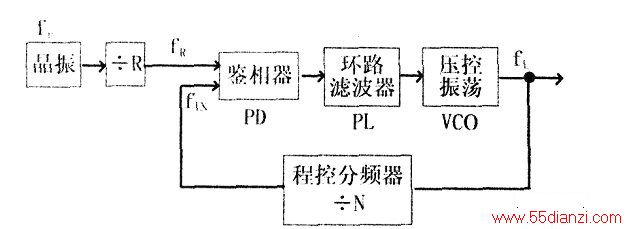

PLL锁相环路主要由:鉴相器(PD)、环路滤波器(实际为低通滤波器LP),压控振荡器(vc0)和可变程控分频器(N)等构成。其原理方框图如下图所示。

图中鉴相器又称为相位比较器(PD),其作用是:

输入的基准振荡频率fR(由晶振频率fr经R次分频得到fR=fR/R)与PLL环路压控振荡器输出的锁相频率(即从本振频率中获取的比较信号f1),经CPU程控分频器分频f1/N)后得到的反馈信号频率f1N,这两个信号在鉴相器中进行相位比较。若两者有相位差,则相位比较器输出误差信号,送到环路滤波器。

环路滤波器(低通滤波器LP)的作用是:对误差信号进行平滑滤波并消除环路中的高频分量和噪声后得到的误差电压(vφ),送到压控振荡器。

注意;PLL环路在锁定时必须要得到一定的控制电压,即:PLL环路作用必须有相位差,相位差维持着两个信号的同步,使输出信号频率稳定。

压控振荡器(vco)就是电压控制振荡器,其振荡频率受环路滤波输出电压(实际为调谐电压Vφ)控制,使压控振荡器输出信号的频率(F1)和相位向输入信号(即基准振荡信号)的频率fR,和相位靠拢,产生正确(同步)的频率和相位。

当PLL环路锁定时,则有:

式中fR是由石英晶振R次分频得到的,因此用锁相环得到的锁相频率f1N具有与石英晶振相当的稳定度。由于R(或fR)为固定数,故f1NaN(即f1N正比于N)。

这样,当要接收某一频率信号时,只要改变程控分频器的分频系数N即可。

程控分频器的分频系数N由CPU提供(CPU还提供接收频道相应的频道选择数据),分频电路典型输出频率为fl/N=fLVPLL锁相环频率合成技术,在自动频率控制和频率合成式高频调谐器中,被得到广泛应用。

上一篇:小数N分频锁相环应用分析