本文设计了一种宽频率范围的CMOS锁相环(PLL)电路,通过提高电荷泵电路的电流镜镜像精度和增加开关噪声抵消电路,有效地改善了传统电路中由于电流失配、电荷共享、时钟馈通等导致的相位偏差问题。

设计了一种倍频控制单元,通过编程锁频倍数和压控振荡器延迟单元的跨导,有效扩展了锁相环的锁频范围。该电路基于Dongbu HiTek 0.18μm CMOS工艺设计,仿真结果表明,在1.8 V的工作电压下,电荷泵电路输出电压在0.25~1.5 V变化时,电荷泵的充放电电流一致性保持很好,在100 MHz~2.2 GHz的输出频率内,频率捕获时间小于2μs,稳态相对相位误差小于0.6%.

锁相环(phase-LOCked loop,PLL)是一个闭环负反馈系统,能够准确地产生一系列与参考频率同相位的频率信号,是现代通信及电子领域中必不可少的系统之一,通常被用于频率合成、同步信号产生、时钟恢复以及时钟产生等。电荷泵锁相环(charge pump phase-locked loop,CPPLL)因其自身所具有的开环增益大、捕获范围宽、捕获速度快、稳定度高和相位误差小等优势,现已广泛应用在无线通信领域中。

1 系统结构及工作机理

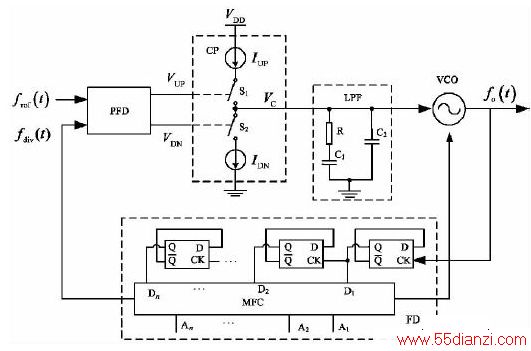

电荷泵锁相环通常由鉴频鉴相器(PFD)、电荷泵电路(CP)、低通滤波器(LPF)、压控振荡器(VCO)以及分频器(FD)构成。本文设计的锁相环系统结构如图1所示,环路具体工作原理为:通过检测PFD输入端的参考信号fref与环路反馈信号fdiv的相差和频差,输出相应的电压信号VUP和VDN,来控制CP的工作状态。电荷泵电路将UP和DN信号转换为压控振荡器的控制电压VC输出。VC通过LPF滤除高频分量,输出直流电平,最终作为压控振荡器的控制信号。随着鉴频鉴相器的两路输入信号间的频差与相差不断减小,VC为某一恒定的电压值时,环路达到锁定状态。

图1 电荷泵锁相环结构

设计时增加了倍频控制(multiple Frequencycontrol,MFC)模块,与分频器和压控振荡器配合使用,通过控制位的逻辑输入,一方面可以编程锁频倍数,控制整个环路的倍频数;另一方面可以控制VCO差分延迟单元的跨导,从而改变VCO的电压增益调节其输出范围。

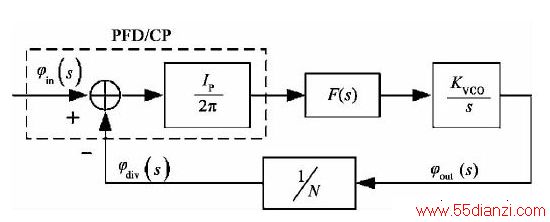

图2 给出了图 1电路的线性等效模型。图中:Ip为电荷泵电流;F(s)为滤波器传输函数;KVCO为压控振荡器的增益;N为分频比;φin为输入参考相位;φout为输出相位;φdiv为分频后的反馈相位。

图2 电荷泵锁相环线性等效模型

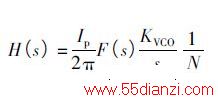

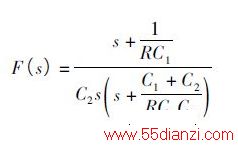

可推出整个系统的开环传递函数H(s)为

式中s为拉普拉斯变换式中的复变量,滤波器传输函数F(s)可以进一步表示为

式中:R,C1和C2分别是图1中相应的电阻和电容值。由式(2)可以看出滤波器传输函数F(s)为二阶线性系统,对于二阶线性系统来说,其传输函数的分母可以表示为ζ2+2ζωn+ωn2,其中ωn是固有频率,ζ是阻尼系数。设计时为了减少环路的抖动,同时保证环路工作的稳定性,一般将环路固有频率ωn设计为参考频率的1/10~1/20,阻尼系数ζ设计为0.3~0.7.

2 电荷泵电路设计

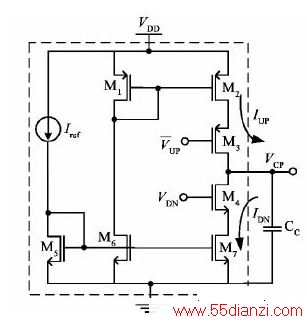

传统的电荷泵电路如图3所示,电流源Iref通过电流镜像为M2和M7提供与Iref成比例的镜像电流IUP和IDN.PFD的输出逻辑信号VUP和VDN控制开关管M3和M4的导通与关断,M3和M4交替导通给滤波电容CC充放电得到电荷泵输出电压VC.然而,由于MOS器件以及电路结构所具有的一些非理想因素,该电路存在充放电电流失配、电荷共享和时钟馈通等问题。

图3 用于锁相环的传统电荷泵电路

传统电荷泵电路的充放电电流是由普通电流镜提供的,其中M1和M2构成充电电流镜,M5和M7构成放电电流镜,理想的情况是充放电流能保持一致。然而工作在饱和区的电流镜MOS器件受到沟道长度调制效应的影响,镜像电流会随源漏压差的变化而变化。具体来说,一方面,M6和M7的镜像电流会因它们的漏极电压不同而不同,进而造成电荷泵充放电电流不同;另一方面,VC电压在一定范围内变化时,M2和M7输出的充放电电流也不能保持一致。

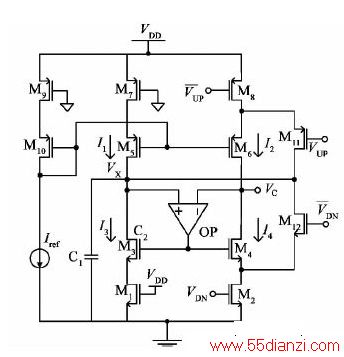

由于电流失配所造成的相位误差可表示为

式中:ICP是设定的电荷泵电流大小;ΔICP为电荷泵的失配电流;Δton是PFD电路产生的导通时间;Tref为基准周期。从上式可以看出,电流失配值对相位误差的影响是成正比关系的,因此,消除电荷泵电路中的电流失配就显得尤为重要。

在电荷泵充放电周期中还存在电荷共享和时钟馈通现象的影响。在充电时M3导通,M2的漏端电压降低到VC值,同时M4关断,M7的漏端电压降低到零;在放电时M3关断,M2的漏端电压升高到VDD值,同时M4导通,M7的漏端电压升高到VC值。由于M2和M7的漏极存在寄生电容,其在充放电周期中就会吸收和释放电荷,因此会影响电荷泵的输出,这一现象称为电荷共享。另外,在充放电周期中,M3和M4栅极寄生电容在时钟信号的驱动下也会产生电荷的释放和吸收现象,从而影响电荷泵输出,这一现象又称为时钟馈通。

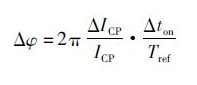

针对传统电荷泵电路中存在的电流失配、电荷共享和时钟馈通的问题,本文提出了一种改进型的电荷泵电路,如图4所示。

图4 用于锁相环的改进型电荷泵电路

如图4所示,首先为了抑制开关管时钟馈通现象,将开关管M8和M2与电流镜管M6和M4的位置进行交换,这样可以有效降低开关管漏极电压的变化幅度。同时,增加了开关管M1,M7和M9来分别匹配M2,M8和M10,以消除电流镜像的误差。

此外,增加的开关管M11和M12分别与M8和M2反相导通,这样就可以抵消时钟馈通和电荷共享现象产生的电荷。

针对电流镜失配的问题,采用了负反馈的方式来抑制充放电电流镜的失配。具体做法是,M5,M6和M10构成电流镜将基准电流Iref镜像后由M6输出电荷泵的充电电流。M5的漏极电流流过M3,然后M3与M4构成的电流镜由M4输出电荷泵的放电电流。放大器OP的引入,在VX节点形成负反馈,就可以严格保证VX=VC,这样几乎完全消除了电流镜漏极电压的不同带来的充放电电流失配问题。

另外,开关管M11和M12的漏极连接到了VX节点,因为VX=VC,所以M11和M12的漏极电压也等于VC,这样做既匹配了时钟馈通和电荷共享现象产生的电荷,又避免了M11和M12的漏极直接连接到VC对电荷泵输出的影响。

放大器OP采用了轨对轨结构,以保证输入和输出电压的摆幅范围,以增大电荷泵输出电压的线性范围。电容C1的引入,既具有稳定负反馈环路的作用,又起到滤波VX电压毛刺干扰的作用。

3 其他模块电路设计

3.1压控振荡器

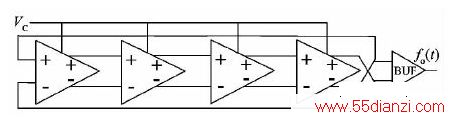

由于折叠式差分环形压控振荡器的电路结构简单、控制线性度好和噪声小,所以本次设计的压控振荡器采用四级差分延时结构来实现,电路结构如图5所示。

图5 压控振荡器电路

压控振荡器差分延时单元如图6所示。延迟单元的线性度和延迟时间范围决定了压控振荡器的线性度和频率范围。为了最大化利用电荷泵输出电压的范围,以提高锁相环的噪声抑制能力,在压控振荡器延迟单元设计上采用了分段线性的方式,将延迟时间分成三段控制。控制电压VC分别控制MOS管M7,M8和M9的栅极电压,以形成3路不同电流来控制延迟单元的线性范围。其中M10,M11和M12作为开关管由图1中的MFC单元产生逻辑信号进行控制,根据频率范围的不同选择其中一路的电流路径。为了改善受控电流随控制电压VC的线性度,为M7,M8和M9增加了源极负反馈电阻,经验证优化的阻值分别为0.4,5和50kΩ。另外,为了提高压控振荡器的工作频率,增加了M7的管子个数,设计中选取M7的管子个数是M8和M9的4倍。此外,延迟单元的最后一级增加了一缓冲级,将双端输出转换为单端输出。

本文关键字:锁相环 锁相环电路,单元电路 - 锁相环电路

上一篇:PLL译码电路