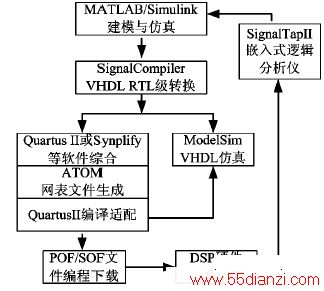

1.基于DSP Builder的设计流程

图1 是基于DSP Builder 开发DSP 系统的设计流程[4,5]。首先调用DSP Builder 工具包中的元件构建电路模型。电路模型建立以后再进行系统级的仿真。仿真通过以后运行SignalCompiler 将模型文件转化成RTL 级的VHDL 代码。转化成功以后,再调用VHDL 综合器进行综合生成底层网表文件。然后调用QUARTusII 进行编译,QuartusII 根据网表文件及设置的优化约束条件进行布线布局和优化设计的适配,最后生成编程文件和仿真文件。生成的POF/SOF FPGA 配置文件用于对目标器件的编程配置和硬件实现。仿真文件主要是用于QuartusII 的门级仿真文件和用于ModelSim 的时序仿真文件和VHDL 仿真激励文件,用于实时测试DSP系统的工作性能。

图1 基于DSP Builder 的设计方法

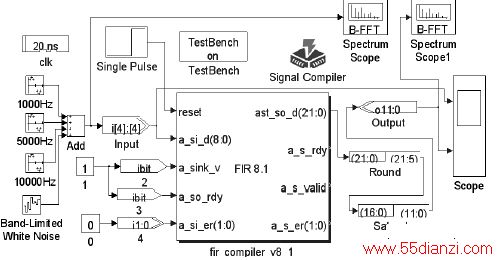

调用FIR 滤波器IP 核以及DSP Builder 中的相关元件,构建了FIR低通滤波器的仿真模型,如图2 所示。如图2 所示,输入信号频率为200Hz、1000Hz、2000Hz 正弦波和宽带白噪声叠加而成的信号。

图2 FIR滤波器仿真模型

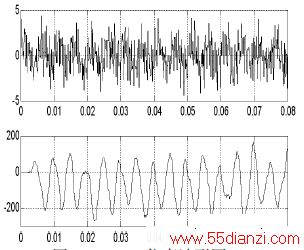

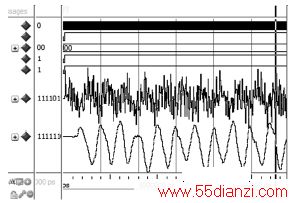

图3 Simulink 仿真波形图

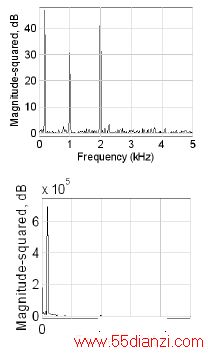

仿真以后,此信号经过截止频率为500Hz 的低通滤波器滤波以后,1000Hz 和2000Hz 的高频正弦波均被较好的滤除了。滤波前后的时域波形图如图3 所示。图4 是滤波前后信号的频谱图。可以看出,此16阶的滤波器滤波性能符合要求。

图4 滤波前后频谱图

3.结果分析

图5 FIR低通滤波器RTL仿真波形

仿真通过以后,再运行Signal Compiler 将此模型转换成RTL 寄存器传输级的VHDL 硬件描述语言。再用Modelsim 软件进行寄存器传输级仿真。仿真结果如图5 所示。

可以看出,经过对转换后的VHDL 语言进行时序仿真,滤波效果良好,进一步验证了模型的正确性。在此基础上,调用QUARTusII 软件进行逻辑综合与适配,最终在Cyclone II 系列EP2C35F672C8 芯片上获得了最高响应速度为151.88MHz 的高速FIR 低通滤波器。资源使用情况:逻辑单元1347 /33216(4%),全部组合逻辑872/33216(3%),专业逻辑寄存器1231/33216(4%),引脚29 /475(6%),总存储位41160/483840(9%)。

4.结论

FIR 滤波器的设计与FPGA 高速实现一直是信号处理领域研究的热点,本文利用FIR 有限冲击响应滤波器IP 核,设计了截止频率为500Hz 的FIR 低通滤波器,在Simulink 中建立了仿真模型并进行了仿真。最终在EP2C35F672C8 型号FPGA 上得到了最高响应频率为151.88MHz 的高速FIR 低通滤波器。设计效率和滤波器性能得到了极大的提高。

本文关键字:滤波器 滤波-陷波电路,单元电路 - 滤波-陷波电路