����˷���Ӱ��ת��Ч�ʵĹؼ�����ʹ�ò��ұ��������˸���˷������㣬ʹת��Ч�������1����������Ҫ֧�ָ����ʽ30f/sʵʱת����ת��ʱ��Ҫ����33ms����֮���ݴ洢����ʱ���ò��ұ�����ת��ģ���DZ�Ҫ�ġ��ò��ұ���ʵ�ֵ�ģ��ṹ��ͼ6��ʾ��

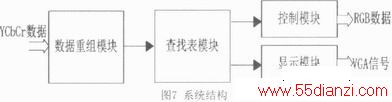

ͨ������RAM1��RAM5������ұ�ӳ�䵥Ԫ����������źŷֱ�ʽ(4)�ķ�ʽ�����RGB��Ӧ�Ľ����ֱ������ʾ����Ĵ����������õIJ���ƽ̨��Altera DE2-70�����壬ϵͳ�ṹ��ͼ7��ʾ���ڲ���Ҫ��Ϊ��������ģ�顢���ұ�ģ�顢����ģ�����ʾģ�顣��������ģ����ͨ�����ò�ͬ�ķֱ��ʺ�YCbCr��ʽ��YCbCr���ݷֱ���ȡ����������FIFO�У����ұ�ģ�鸺��ͨ��FIFO��Y��Cr��Cb��ֵ�������˷������������ټӼ���������ת����RGB24λ��ֵ������ģ�鸺����������IJ��š���ͣ�ʹ洢�طŵ���չ���ܡ���ʾģ�鸺������������VGA��ʾ��

2.2 ϵͳ��֤

2.2.1 ������֤

ϵͳ��֤�����������֣�����Ҫ��֤��ͬ��ʽ��YCbCrת��ΪYCbCr444����������ȷ�ģ��ⲿ�ֿ�������ModelSim��ת�������з��棬�ֱ��Y��Cb��Cr�������ݰ�˳����ڶ�Ӧ������FIFO�С�

֮��ͨ��MATLAB�����ݱȽ�����strcmp����FIFO�е�YCbCr444������MATLABת�������ݽ��бȽϡ��ֱ�ʹ��QCIF��CIF��HDTV���ֱַ��ʽ������һ֡��������֤������ֵ��Ϊ1��֤��ת��ϵͳ�ɿ���

ϵͳ����ͨ��ModelSim��������ͼ8��ʾ��

��ͼ8�У�adr_y��adr_u��adr_v��Ϊ����������YCbCr��ַ��y_in��Cb_in��cr_in�ֱ�Ϊ��ת�������ݣ�R_out��G_out��B_outΪת�������������ena_in��ena_outΪ����ʹ�ܺ����ʹ���źţ��������źſ��Կ�����Ƶת����������ֹͣ����2��ʱ������֮��Ϳ�������ʾ������֣��������Ҫ6 μs�����۸����о������ӳ٣��������ڶ�ת���ٶ�Ҫ��ϸߵ�ϵͳ�ϡ����ؼ�����Ϊcn����һ֡ͼ����ȫת����֡������counter�����һ�Σ�ͨ�����������ȡ������һ֡ͼ����м��顣

2.2.2 FPGAϵͳ��֤

������ϵͳ��¼��FPGA�н���Ӳ����֤���������Ƶ����ͨ��SD������ϵͳ������YCbCr��ʽ�����飬����ѡ�������ָ�ʽ���ֱַ��ʵ���Ƶ���룬��ͼ9��ʾ�ֱ�ΪYCbCr420��ʽOCIF�ֱ��ʡ�YCbCr422��ʽCIF�ֱ��ʺ�YCbCr444������ʽHDTV�ֱ���ͨ��YCbCr-RGBת����ijһ֡ͼ�����ʾ�������ʾ��������÷���������ȷʵ��30f/s�IJ�ͬ��ģ�Ͳ�ͬ��ʽ��YCbCr-RGBʵʱת����

3 ����

���Ļ���FPGA����Ӳ��ƽ̨��ʵ�ֲ�ͬ�ֱ��ʺͲ�ͬ��ʽ��YCbCr��Ƶ���ݵĴ洢��������VGA��������нṹ���ա��������ơ�������ϵͳ�ȶ����ص㡣��Ƶ��ʽת�����������ڴ���Ƶͼ������ͨ��ƽ̨��������Ƶͼ��߾��ȿ���ʵ��ת������ʾ��Ҫ��Ӧ���ڶ�����ʽ��Ƶ��������������ӿ����ݸ�ʽ��ƥ��ij��ϣ�����һ����Ӧ�ü�ֵ��

���Ĺؼ��֣���ģ �����Ӧ��������֪ʶ���� - �����Ӧ��