在修改MPAX 表项之前需要先执行如下操作:

1. 将MPAX 表项对应的存储空间内容从cache 中剔除出去。即使对于属性为不可写的存储空间,应该使用CACHE_wbInvL2()而非CACHE_inv L2()。

2. 如果对受影响的存储器空间使能了预取功能,则需要对预取缓存执行失效操作。

3. 执行“MFENCE”确保回写及失效操作完成。

CorePac 的MPAX 寄存器受CorePac 的内存保护寄存器锁保护。SES 及SMS 的MPAX 内存保护属性寄存器被MSMC 内部分别用于SES 及SMS 的锁保护。MSMC 内部其他寄存器被MSMC内部用于非MPAX 的锁保护。

2.3 外设配置端口保护 – MPU

关于MPU 的基本信息参考“KeyStone Architecture Memory Protection Unit User Guide (SPRUGW5)”。

MPU0、MPU1、MPU2 及MPU3 对所有KeyStone 1 器件是相同的。但是对于不同的器件,其附加MPU 的个数,每个MPU 支持的地址范围表项数,MPU 的默认配置均有所差异。具体可参考相关器件手册的“内存保护单元(MPU)”章节。

MPU 与MPAX 的区别在于,如果访问地址不在MPU 任何一个地址范围内,则该地址访问是允许的;而当该地址与MPAX 中任意表项地址范围不匹配时,则该地址访问被拒绝。

注意,如果没有被MPPA 的设置所拒绝,MPU 单元默认所有的访问都是许可的。对于一个地址访问,MPU 首先将访问的权限ID 与MPPA 寄存器的AID bit 配置进行核对,如果与权限ID 对应的AID bit 为0,则不需要核对地址范围,该访问被许可。如MPPA=0 则允许所有的对该空间的访问,如果要拒绝任意对该空间的访问则需要将MPPA 配置为0x03FFFC00。L1 及LL2 内存保护的MPPA 设置则有所不同,当MPPA 中AID bit 为0 是拒绝相应的访问。

当传输与MPU 中多个地址范围匹配时,所有重叠的范围必须允许其访问,否则该访问会被拒绝。最终赋予的访问权限与所有匹配表项中最低的权限等级一致。如某传输与2 个表项匹配,其中一个是RW,另一个是RX,则最终的权限是R。这与MPAX 也是不一样的。如果一个地址落入多个MPAX 表项,编号高的表项优先于编号低的表项。MPAX 只会用编号最高的表项决定权限,并忽略其他匹配的表项。

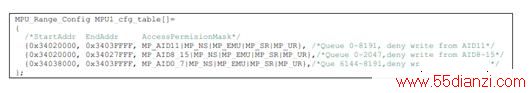

如下与本文对应例程中一个对MPU1 的配置例子。每行代表MPU 中一个配置范围。

如上配置知,队列保护如下:

· 队列0~2047 只可由AID0~7 进行写(PUSH)操作;

· 队列2048~6143 可由AID11 以外所有的AID 进行写(PUSH)操作;

· 队列6144~8191 只可由AID8~15(AID11 除外)进行写(PUSH)操作。

TCI6614 上的MPU6 用于避免ARM 对DDR3 的非法操作。注意,MPU6 是用于低32-bit DDR 物理地址范围的保护。

注意,为了清除MPU 异常/中断事件,必须在服务程序的最后向EOI 寄存器写0.

TCI6614 的MPU 事件与其他KeyStone 器件有所不同。TCI6614 中所有的MPU0~7 事件被合并为一个事件并作为一个系统事件连接到CIC0。由于TCI6614 MPU 事件是电平中断而非脉冲中断事件,所有必须首先清除MPU 事件标志,然后才可以清CIC 标志。对于脉冲中断事件,必须首选清CIC 标志,然后清源标志。

另外,只有在通过PSC 使能BCP 后,才可以访问TCI6614 中用于BCP 的MPU5。即在访问TCI6614 中MPU5 寄存器时,如果此时BCP 没有被使能,则该访问将触发访问错误。

2.4 预留区域保护

预留区域(非法地址)被自动保护。对非法地址进行读操作时将返回垃圾数据,写操作则会被阻止。对预留区域的访问可以产生异常,这有益于捕获软件bug。

由于DSP core 的访问会经过L1D 控制器,所以DSP core 对非法地址的访问会触发L1D 内存保护异常。

DSP core 从非法地址执行时将触发指令获取异常。

对于非法写操作,触发的异常取决于相应的目的地址。

DMA 对非法地址访问时,DMA 模块会上报总线错误。DMA 错误事件可以作为异常路由到DSP core。

3 EDC

EDC(Error Detection and Correction)用于存储器软错误 (SOFt Error) 。软错误是一个错误的信号或数据,但是并不意味着硬件被破坏。在观测到一个软错误后,并不意味着系统可靠性会下降。在宇宙飞船中这种类型的错误称为单一事件扰乱。在内存系统中,一个软错误会改变程序中的一条指令或者一个数据值。软错误通常可以通过器件的重启进行纠正,而硬件错误通常不能通过重启来恢复。软错误不会对系统硬件造成破坏;仅仅会对处理的代码或数据造成错误。产生软错误的原因有:

1. 阿尔法粒子辐射及宇宙射线产生能量中子及质子。发生的概率取决于器件的地理位置及周围环境。通常,一个器件在几年中才会出现几次。

2. 软错误也可由随机噪声、干扰或信号完整性错误引发,如板载电感应或电容串扰。如果软错误发送概率高于上述条目1 中的理论值,则应该检查硬件设计找出其他原因。一个常见的原因是供电电源电压低于预期,导致器件对噪声或干扰的影响更敏感。

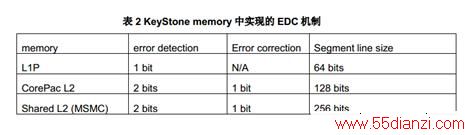

KeyStone 器件各级memory 中都实现了EDC 机制,下表对不同memory 模块的实现机制进行了比较。

3.1 L1P 错误检测

关于L1P 及LL2 EDC 基本信息参考“TMS320C66x DSP CorePAC User Guide(SPRUGW0)”。

校验比特生成与核对:校验比特在进行64-bit 对齐的DMA 写或L1P cache 缓存时生成。非64-bit对齐的DMA 访问将使校验信息失效。在256-bit 对齐的程序读取或64-bit 对齐的DMA 读操作时,L1P EDC 逻辑会核对校验信息。

错误检查设置:器件复位后默认情况下L1P 错误检查特性是关闭的。一旦L1PEDCMD 寄存器中的“EN”bit 被置位,所有L1P memory 中的ED 逻辑被使能。下面是从应用代码中摘录的L1P ED 功能使能例子。

注意:要使L1P ED 功能工作正常,必须同时使能L2 EDC。

对L1P cache 访问时的错误处理: 对从L1P cache 中获取程序产生的校验错误,没有专用的系统事件,然而,错误检测逻辑会发送一个直接的异常事件给DSP(IERR.IFX 事件),然后用户可以使用内部异常事件获取这个错误。L1PEDSTAT 寄存器的PERR bit 会被置位。L1PEDARRD寄存器会记录包含错误bit 的的地址信息。在L1P 错误对应的异常处理服务函数中,需要对包含错误地址的cache line 进行失效操作。

对DMA 访问的错误处理:对DMA/IDMA 访问产生的校验错误,对应#113 号系统事件。用户可以使用这个事件获取错误。L1PEDSTAT 寄存器的DERR 比特位会被置位,并且L1PEDARRD 寄存器会记录包含错误bit 的地址信息。

L1P EDC 功能验证:通过置位LPEDCMD 寄存器中的SUSP 比特可以暂停L1P EDC 逻辑。使用该特性,可以软件模仿EDC 错误并验证EDC 功能。与本文对应的例程中提供了验证L1P EDC功能的代码,对应函数L1P_ED_test()。

3.2 LL2 错误检查与纠正

校验比特生成与核对:在对L2 以128 bits 为单元进行内存写操作时会产生相应的校验信息。非128-bit 对齐或者小于128 bits 的写操作会使校验信息失效。对128-bit 对齐的memory 读操作时,LL2 EDC 逻辑会核对校验信息。更多信息参考“TMS320C66x DSP CorePac User Guide(SPRUGW0)”。

错误检查及纠正配置:器件复位后默认情况下LL2 EDC 特性是被关闭的。与某些C64+ DSP 不同的是,KeyStone DSP 不能对内存分块使能EDC。一旦EDC 使能,EDC 逻辑对整个CorePac L2 内存生效。然而,可以对不同的内存访问请求者分别使能,如L1D 控制器、L1P 控制器或DMA 控制器。例如,如果用户只需要对代码段使用EDC,需要使能下面三个域:

1. 设置L2EDCMD 寄存器中的EN bit 以使能LL2 EDC 逻辑;

2. 设置L2EDCEN 寄存器中的PL2SEN 比特以使能L1 SRAM 的EDC 逻辑对L1P 访问的检查;

3. 设置L2EDCEN 寄存器中的PL2CEN 比特以使能L2 cache 的EDC 逻辑对L1P 访问的检查。

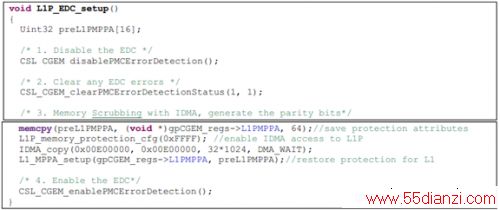

从关闭到使能状态转变时,LL2 EDC 逻辑不会初始化校验RAM。因此,在进入使能状态后,校验RAM 中的值是随机值,需要用户软件对其进行初始化,。对L2 EDC 的配置必须遵循“TMS320C66x DSP CorePac User Guide(SPRUGW0)”中阐述的EDC 配置顺序。下面是从例程中摘录的L2 EDC 使能函数参考代码:

本文关键字:暂无联系方式计算机应用,电子知识资料 - 计算机应用

上一篇:开放式数控系统及其应用分析