对来自L1D 控制器的访问错误处理:在经过L1D cache 从LL2 中获取数据时,对所有这些数据会进行错误检查,但是不会有任何的纠正。不管是1-bit 或者是多bit 错误,将会通过#117 号系统事件(L2_ED2:不可纠正比特错误检测)上报给DSP core。

对来自L1P 及DMA 控制器的访问错误处理:1-bit 错误可以被纠正并通过#116 号系统事件(L2_ED1:可被纠正的比特错误)上报 。2-bit 错误可以被检测,并通过#117 号系统事件上报该错误。

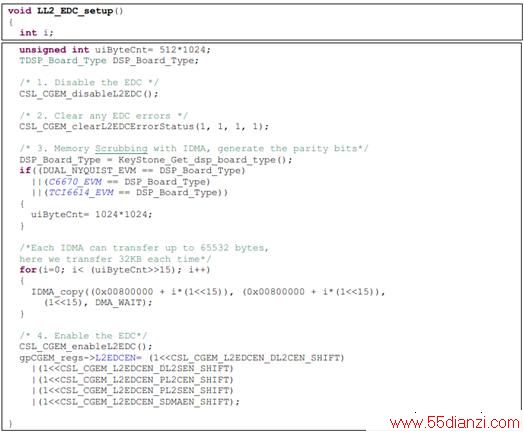

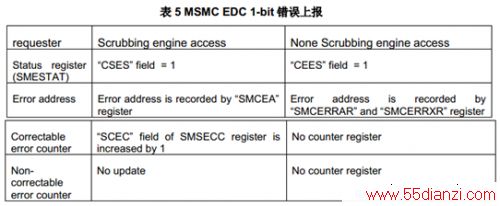

下表列出对于不同存储器访问请求者,相应的1-bit 错误处理细节。

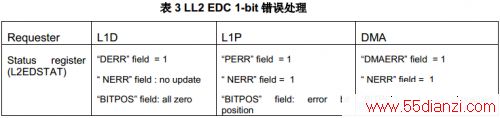

错误计数器(L2EDCPEC, L2EDNPEC)非常有用,可用于在长时间运行的系统中评估校验比特错误发生的种类与概率。

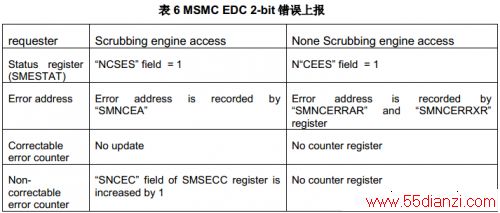

下表列出对不同存储器访问请求者,相应的2-bit 错误处理细节。

对于大于2 bits 的错误,EDC 逻辑可能会检测并报告为1-bit 或2-bit 错误,或者EDC 根本检测不到该错误。所以说,KeyStone 系列EDC 硬件逻辑只能保证检测2-bit 错误或纠正1-bit 错误。

通常软错误出现的概率很低,首先出现1-bit 错误,在相对长时间后,第二个错误bit 也许会产生。由于1-bit 错误可以被纠正,而2-bit 错误不能被纠正,所以我们应该尽可能在第二个比特错误出现前纠正好第一个比特错误。

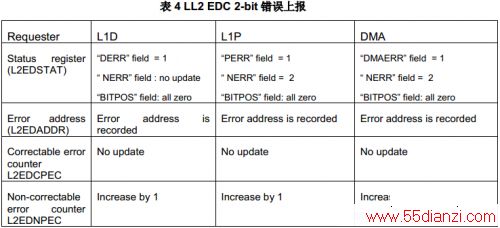

纠正1-bit 错误的操作通常称为“刷新”。 为了刷新一块存储器,可以使用IDMA,把IDMA 的源地址与目的地址设为相同的地址;字节长度设置为期望覆盖的内存块。地址访问必须是128-bit 对齐,并且整块的内存范围长度必须是128 bits 的整数倍。在IDMA 从LL2 读取数据时,对于存在有效校验信息的128-bit 字,EDC 硬件会纠正可能存在于其中的1-bit 错误。当IDMA 把数据回写到相同的地址时,EDC 会对数据产生校验信息并标识其为有效。

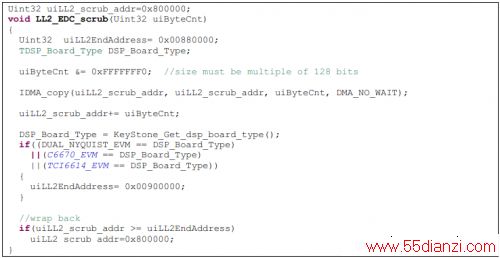

刷新操作通常是在1-bit 错误中断服务函数中进行。但是在1-bit 错误发生之后2-bit 错误发生之前,某些数据也许不会被访问,在没有访问时1-bit 错误是不会被自动上报的。为了避免这种情况,应该周期性地刷新整块存储器区间来纠正潜在的1-bit 错误。下面是一段LL2 EDC 刷新的代码例子。

通常,这个函数可以在一个定时中断中调用。如在一个600 秒周期的定时中断中调用该函数。

![]()

这样, 1MB 的存储区间会每7 天被刷新一遍。

由于刷新操作会与正常的内存操作相竞争,因此会影响正常内存操作的性能。所以刷新操作不能太频繁,但是必须在2-bit 错误产生前完成。在设计时必须权衡考虑。

LL2 EDC 功能验证:通过设置L2EDCMD 寄存器中的SUSP 比特可以暂停LL2 EDC 逻辑。使用该特性,可以软件模仿EDC 错误并验证EDC 功能。与本文对应的例程中提供了验证LL2 EDC 功能的代码,对应函数LL2_ED_test()。

3.3 SL2 错误检测与纠正

对共享存储器SL2 的基本信息,参考“KeyStone Architecture MultICore Shared Memory Controller User Guide(SPRUGW7)”。

校验比特产生与核对:有两种机制用于MSMC 校验信息的产生与检测:

1. 对任意master 发起的256-bit 内存段的写操作时,校验信息会被更新并设置为有效。小于256 bits 的写操作会使校验信息失效。当DSP master 发起256-bit 内存段的的读操作时,校验信息会被检查。

2. MSMC 包含一个后台错误纠正硬件称作刷新引擎,用于周期刷新存储器的内容。刷新的周期数可以通过SMEDCC 寄存器中的REFDEL 比特域来配置,每次刷新会读取并回写大小是4 个32字节的块。在检测并纠正1-bit 或者检查到2-bit 错误时,刷新引擎还会上报EDC 错误。在MSMC用户手册中有具体的机制细节描述。

DSP 复位后,MSMC 硬件会使校验信息失效,并重新初始化校验信息。在第一次读MSMC 存储器时,软件必须先检查SMEDCC 中的PRR 比特(校验RAM 是否准备好的状态信息)。

错误检测与纠正配置:DSP 复位后SL2 EDC 逻辑的刷新引擎被使能,并且会在后台产生校验信息。软件不需要像LL2 EDC 一样使用DMA 进行存储器刷新,只需要查询SMEDCC 寄存器中的PRR(校验RAM 准备)比特位来确认校验比特已经产生。为了使能错误纠正,SMEDCC 中的ECM比特同样应该使能。请注意,错误纠正逻辑会对从SL2 的读操作增加1 cycle 的时延(访问流水线增加了一级),不过访问吞吐量并不会降低。

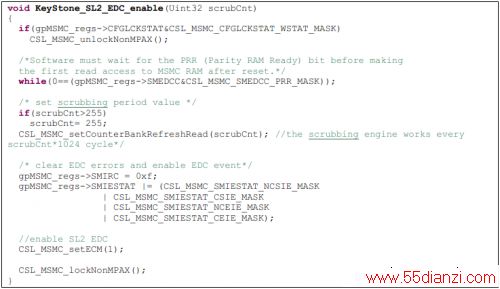

下面是使能MSMC EDC 功能的例程:

错误上报机制:MSMC 用户手册中有详细的错误上报机制信息,这里总结如下表。

请注意,由刷新引擎上报的错误地址是从0 开始的地址偏移,而为非刷新访问记录的错误地址是器件中从0x0C000000 开始的SL2 地址。

MSMC EDC 功能验证:可以通过设置SMEDCTST 寄存器中的PFn 比特位(bit0~3)来暂停MSMC EDC 逻辑。SMEDCTST 的地址偏移是0x58。每个SL2 RAM bank 对应PFn 中一个比特(PF0~3 与bank0~3 依次对应),每个比特可以用于禁止对校验RAM 的写操作。这样可以冻结bank 对应的校验RAM,因此可以通过故意注入错误来破坏SL2 存储内容与校验信息的一致性,从而测试检测纠正逻辑。具体的顺序如下:

1. 向测试bank 中的某一个位置写一个已知值,这样可以正确地为这个位置初始化一个校验值。

2. 向SMEDCSTST 对应的PF 比特写1 以冻结该校验值。

3. 向上述被写的位置写任意字节来改变该位置的数值,如果检验纠正功能则写一个1-bit 差异的值,如果检验检测功能则写一个存在2-bit 差异的值。此时该位置的校验值与其存储的数值没有同步。

4. 读回该位置的值,将会产生所选类型的校验错误。

与本文对应的例程中提供了相应的代码用于验证SL2 EDC 功能,对应的函数为SL2_EDC_test()。

4 其它鲁棒性特性

4.1 看门狗定时器

对应看门狗定时器的基本知识,请参考“KeyStone Architecture Timer64 User Guide(SPRUGV5)”中“看门狗定时器模式”章节。

定时器0~(N-1)可用于N 个core 的看门狗。在TCI6614 中定时器8 是ARM 的看门狗定时器。

在看门狗模式下,定时器倒计时到0 时产生一个事件。需要由软件在倒计时终止前向定时器写数,然后计数重新开始。如果计数到0,会产生一个定时器事件。看门狗定时器事件可以触发本核复位、器件复位或者NMI 异常,这可以通过配置相应器件手册中描述的“复位复用寄存器(RSTMUXx)”来选择。

使看门狗事件触发NMI 异常具有更高的灵活性,在NMI 异常服务函数中,错误的原因及某些关键的状态信息可以被记录下来,或者上报给上位机来进行故障分析,然后如果它不能自恢复则可以再由软件来复位器件。

4.2 EDMA 错误检测

关于基本的EDMA CC 错误信息可以参考“KeyStone Architecture Enhanced Direct Memory Access(EDMA3)Controller User Guide(SPRUGS5)”中的“错误中断”章节。

本文关键字:暂无联系方式计算机应用,电子知识资料 - 计算机应用

上一篇:开放式数控系统及其应用分析