以STM32F103VET6微处理器为核心,配合CR95HF射频芯片构成符合ISO/IEC 15693标准的便携式读卡器。同时,采用无线存储芯片M24 LR64,开发了与读卡器配套的新型无源RFID标签。该RFID系统工作在13.56 MHz频率,其标签的存储容量达到24 KB,并通过I2C总线实现数据传输,适用于需要在标签中携带大量数据的应用场合。实验证明,开发的RFID系统能稳定地进行无线数据通信,具有工作稳定、适用性强的特点。

射频识别(Radio Frequency IdentifICation,RFID)技术是一种以射频信号为通信载体非接触的自动识别技术,能够实现无线信息交流。RFID技术采用射频信号传输数据,具有非接触和在恶劣环境下工作等优点。此外,相比于其他识别技术,RFID标签能够通过上位机操作读卡器进行读写,更加方便和高效。因此,目前该技术已被广泛应用于交通运输、身份验证、门禁安全等领域。根据供电方式,RFID标签可以分为有源、无源和半有源标签。

本文首先介绍了典型的嵌入式RFID系统,之后以意法半导体公司STM32F103VET6为核心与CR95HF射频芯片组成一个便携式读卡器。同时,针对现有RFID标签存在存储容量小、数据传输方式单一等问题,基于意法半导体提供的M24LR64芯片,研究设计了一款应用于嵌入式RFID系统的大容量无源RFID标签。该读卡器和标签无线工作频率为13.56 MHz,符合ISO/IEC 15693标准,并支持符合I2C总线标准的有线通信;标签存储容量可达24 KB,可以满足方便携带和大容量存储的要求。

1 嵌入式RFID系统介绍

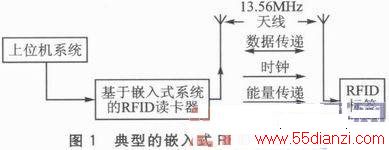

典型的嵌入式RFID系统通常包括以下部分:上位机系统、读卡器、射频标签。读卡器由嵌入式微处理器和射频芯片组成。上位机工作的流程大致分为读写两个部分:读取标签和向标签中写信息。读取标签信息时,上位机发出指令信号存入微处理器,软件控制射频芯片发送读数据命令给标签,标签根据接收到的读数据命令将存储单元中指定的数据通过天线发送到读卡器,读卡器再将数据发送到上位机系统。向标签中写信息时,过程类似,上位机通过射频读卡器发送写指令,并将数据写到所设计标签的相应存储单元。典型的嵌入式RFID系统框图如图1所示。

2 基于嵌入式系统的读卡器和标签的设计

2.1 嵌入式RFID读卡器的设计

2.1.1 读卡器主控芯片及外围电路的设计

本设计主控芯片采用STM32F103VET6微处理器。该处理器基于ARM Cortex—M3内核,支持多种通信总线,工作频率为72 MHz,包括5个USART串行接口、2个I2C总线接口、3个SPI总线接口、CAN总线和USB总线。同时,该处理器还具有80个通用I/O口、A/D转换器、16位定时器、实时时钟等功能,具有功能强大、功耗低等优点,可以满足本系统读卡器的设计要求。

读卡器采用标准USB 5 V供电,通过稳压芯片KF33BDT提供3.3 V电压供微处理器使用。为了抗干扰,微处理器的每个电源引脚都并联了0.1μF的去耦电容。微处理器的外部时钟源选用两个,分别为高速外部时钟源和低速外部时钟源。高速外部时钟源的晶振频率为8 MHz,用于为系统提供精准的主时钟;低速时钟源的晶振频率为32.768 kHz,用于为时钟或日历等提供时钟源。负载电容的选择需要根据晶振的大小进行匹配,本读卡器中高速外部时钟源的负载电容为20pF,低速外部时钟源负载电容为10pF。sTM32F103 VET6微处理器通过串口与CR95HF射频芯片进行通信,采用标准JTAG接口实现程序的烧写与调试,并通过USB总线与上位机高速通信。

2.1.2 读卡器射频电路设计

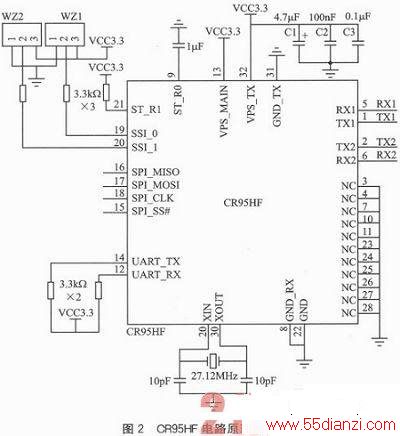

本文设计的RFID读卡器使用意法公司的CR95HF射频芯片。CR95HF是具有SPI和UART串行接入的多协议非接触13.56 MHz射频芯片,支持ISO/IEC14443 A和B、ISO/IEC 15693以及ISO/IEC 18092等协议,能管理读卡器模式的帧编码和译码,可以广泛应用于RFID等近场通信。以CR95HF作为射频芯片,支持高频频段的无源RFID,可以与本文所设计的基于M24LR64的新型大容量标签进行无线通信。CR95HF电路原理图如图2所示。

本设计中的CR95HF使用串口方式与STM32F103VET6微处理器通信,CR95HF提供与串口标准兼容的通信接口(14和12引脚),可与微处理器进行双向通信。CR95HF射频芯片供电电压为3.3V,可以使用STM32F103VET6所用电压。同时,电容C1、C2、C3用来去耦,减少干扰。RX1、TX1、RX2、TX2引脚用来连接匹配电路和天线。CR95HF工作在高频频段,在天线设计上,通过匹配电路电容和电阻值的选取,得到匹配电路的等效电容,由于会和天线电感组成频率为13.56 MHz LC振荡回路,因而可以计算出所需的天线电感,从而得到天线参数,进行匹配设计。

2.1.3 数据通信部分的设计

本文设计的RFID读卡器通过使用STM32F103VET6芯片内部集成的标准USB接口与PC上位机实现有线通信。USB接口支持设备的即插即用和热插拔功能,从而可以方便地实现读卡器设备的移动。同时,USB2.0高速总线传输速率可达480 Mbps,可以快速地将读卡器与PC上位机进行数据交换。由于本文所设计标签具有容量较大等特点,因而读卡器需要能够快速地将读取到标签内的大容量数据传输给上位机,而USB总线传输速率极高的优点使得本读卡器可以满足实时需求。

2.2 基于M24LR64的大容量无源RFID标签设计

2.2.1 大容量RFID标签电路设计

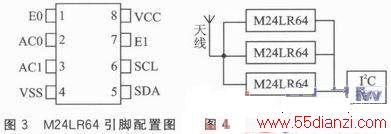

M24LR64是意法半导体公司推出的一款新型无线存储器芯片,其内部具有口令保护的64 Kb EEPROM,支持工作频率为13.56 MHz,符合ISO/IEC 15693协议标准的无线通信接口数据,传输频率为400kHz,符合I2C串行总线标准的有线通信接口。其工作电压为1.8~5.5 V,在I2C总线接口模式下,芯片工作电源由VCC引脚提供,存储器结构为8 192×8位;在无线射频接口模式下,以接收到的射频载波信号为工作电能,存储器结构为2 048×32位。M24LR64引脚配置图如图3所示。

由于该芯片价格比较昂贵,应根据不同的需求选择标签存储容量;根据项目需要,本文设计了采用3个M24LR64芯片的标签,即实现了24 KB的大存储容量标签。另外对三个芯片采用并联方式,从而实现三个芯片共用一条I2C总线和一根天线,减少标签的成本和功耗。

设计中,通过让3个M24LR64的E1、E0引脚依次赋值00、01、10来区分是第几个M24LR64存储器。SCL、SDA为引出的I2C总线接口。同理,当标签采用RFID读卡器对标签进行无线数据读写时,根据3个M24LR64引脚E1、E0的不同来区分和选择所需的M24LR64。其中,AC0和AC1是存储器天线的收发端,将其并联实现了共用一个天线。标签电路原理示意图如图4所示。

2.2.2 天线研究与设计

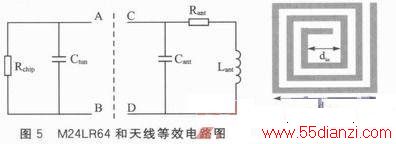

M24LR64在进行无线方式的信息读写时,采用频率为13.56 MHz的高频(HF)载波进行通信。通过电磁耦合,标签利用外部电感天线从嵌入式RFID读卡器的电磁场中获取所需电能。M24LR64等效电路和天线等效电路图如图5所示。其中,Ctun是M24LR64的内部调谐电容,其值为28.5 pF,并联电阻RChip以模拟芯片的电流消耗;天线是一条导线,Rant表示等效电阻,Lant表示天线电感,CANt表示天线寄生电容。

由于在一阶微分方程式中,RChip、CANt、Rant可以忽略不计。因此,M24LR64存储芯片和天线等效于谐振频率为13.56 MHz的LC振荡回路,满足:

![]()

其中f=13.56 MHz,Ctun=28.5 pF,可以计算出一个M24LR64时所需天线电感。由于采用3个M24LR64并联,总电容为单个M24LR64的3倍。求得设计标签所需的天线电感:

![]()

代入数据,可得所设计标签的理想天线电感Lant=1 611.22 nH。

设计天线形状为正方环形天线,如图6所示。