使用综合平台的设计者,通过将寄生效应构建到优化模型中,还能在开始优化时将所有寄生效应包括在内,并借此消除设计过程中的不确定因素。这些模型被构建成能处理与器件及其互连有关的不必要的电阻、电容及电感效应等信号完整性问题。设计者能对相邻连线间互耦这样的效应进行建模,如果这些因素影响到性能,则综合平台中的程序算法将把这些因素考虑到电路布局中。

布局布线

综合平台利用几何程序来控制电路布局,以达到系统性能目标。这些问题涉及到器件、模块、底层规划及布线等。为达到模拟及射频电路所需的性能指标,可考虑以下电路布局布线约束。

对称约束:一个部件可被约束成以水平或垂直轴线为中心;两个同样大小的部件可被约束成相对轴线为镜像。

镜像节点:可围绕轴线对节点进行镜像。

节点匹配:可将标记(布局扩展)增加到布线中,以使两个节点的水平及垂直金属长度整体上均衡。

对齐:两个元件可被约束成互相沿顶部、底部、左或右对齐。

电容约束:这能通过弯曲布线长度来限制布线与基底间的电容。

IR压降约束:布线器将对电源轨道尺寸进行规定,以将IR压降值限制在指定的数值上。

对器件生成器中的另一个重要考虑是中间数字化,这能减少器件电容,并确保有对称的电流方向、保护环(guard ring)及虚拟(dummy)结构等。图3显示了为模拟或射频设计所生成的器件例子。

如何验证模拟设计的鲁棒性

Barcelona公司可保证对每一优化实例的鲁棒性验证都能通过使用验证金字塔来完成,并已将它应用检验0.18及0.13毫米综合平台上。正如我前面所提到的,利用这种验证金字塔使我们既能避免设置及运行Monte Carlo模拟的艰辛,又能避免运行多种硅制造工艺的昂贵。

www.55dianzi.com

我们的验证金字塔分为4层。第1层:我们先基于试验及试探法设计来选择指标规格。设计规格空间由主要指标的无关联扫描来覆盖。在PLL的例子中,就是抖动、功率及静态相位误差。我们将试探性标准用于考虑了各指标相关性的栅格的定义。

我们进行一系列优化来使这一综合平台的功能合格。此过程包括将试验方案的数量从3个增加至49个。试验方案被定义成从1至7选择工艺阶段、将电源从其额定值上变化10%、将片上多晶硅电阻从其额定值上改变20%以及选择三种VCO频率等。

第2层:我们通过检查可从SPICE仿真上提取的参数与从综合平台上预计的参数之间的相关性来从第1级上检验优化设计的精度及功能是否合格。

我们特别强调对模拟电路模块进行SPICE仿真。例如,对于VCO,我们同时在低及高频上对以下内容进行仿真:功耗饱和余量、频率范围、kVCO增益、PSRR、(kVdd)。

第3层:我们期望能提供由综合平台预测的指标规格与在宏观层次上所提取仿真之间的相关性。

为保证指标能准备好用于制造,我们要求该综合平台能产生没有版图与原理图误差的GDSII数据。我们还要求不能违反任何半导体设计规则。

模拟设计中使性能下降或者甚至造成设计失败的一个主要问题是寄生效应。

第3层验证包括对自动GDSII版图的寄生预测。第2层指标选择是基于覆盖频率与低抖动范围、低功率PLL并针对相应的频率范围和覆盖以下应用的硅样片进行,这些应用包括:消费多媒体、无线及有线通信、微处理器及ASIC。

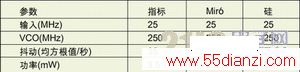

第4层:综合平台验证的最后一步是硅确认。这里的目标是通过硅中的三项合格性验证来确认第1层的严格及鲁棒性。选择第3层设计。表2及表3给出了在TSMC的 0.18 μm逻辑工艺上生产的两种PLL的关键参数。显示结果是针对最差情况下的工艺、电压及温度变化。大约在几小时内即可产生出GDSII版图,且无需任何改动即可直接提交给晶圆代工厂

本文关键字:规格 射频技术-RFID,通信技术 - 射频技术-RFID