1.引言

TMS320F241型DSP是目前应用比较广泛的一款定点DSP,它具有20MIPS的指令执行速度,强大的内部事件管理器、I/O端口和其他外围设备。其中,串行外设接口(SPI)是一个高速同步串行输入/输出(I/O)端口,它允许一个具有可编程长度(1到16位)的串行位流,以可编程的位传送速率从设备移入或移出。SPI通常用于DSP控制器和外部器件或其它控制器间的通讯。

在开发DSP系统时,某些情况下会读取或者存储一些定值,这时我们就需要扩展EEPROM。具有SPI接口的串行EEPROM均可被TMS320F241直接逻辑扩展,方便易行。X5043是Xicor公司最高时钟速率为3.3MHz带有块锁保护的4Kbits的CMOS串行EEPROM。该器件内部组织阵列是X8位,具有串行外围接口(SPI)和软件协议的特点,允许在简单的四线总线上工作;该器件利用Xicor专有的直接写入晶片提供最小为10万次擦写和最少100年的数据保存期。

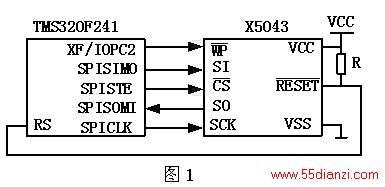

2.硬件设计

X5043与TMS320F241型DSP的连接关系如图1所示。DSP作为主控制器,工作于主模式下,SPISIMO为DSP的数据发送端,连接到X5043的数据接收端(SI);SPISOMI为DSP的数据接收端,连接到X5043的数据发送端(SO);SPISTE配置成I/O口连接到X5043的片选端(/CS);SPICLK为SPI数据传送的时钟信号,连接到X5043的串行时钟端(SCK),串行时钟由DSP控制。DSP的数据在SPISIMO引脚上输出并从SPISOMI上锁存, DSP通过写入SPIDAT寄存器的数据启动SPICLK串行时钟信号从而启动数据传送,当8位串行位流传送完毕后,SPICLK信号中止,传送结束。

3.软件设计

3.1工作模式的选择

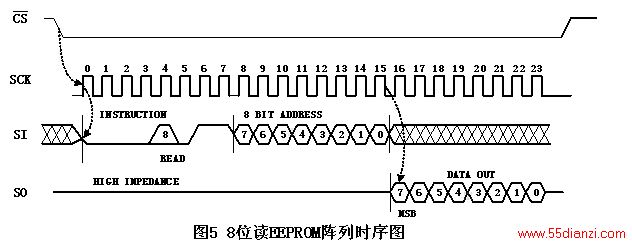

TMS320F241的SPI接口有可选择的四种不同的时钟模式,如何选择时钟模式是它与各种扩展SPI接口器件实现时钟同步的关键。X5043的数据在时钟下降沿从SO引脚上输出并在时钟上升沿从SI引脚上锁存。读操作时,在其从SI引脚输入的最低位地址所对应的时钟下降沿,其SO引脚开始输出数据,如图5所示。

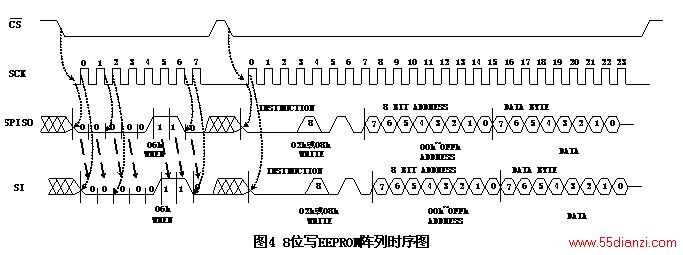

作为主器件的DSP可以选择 ‘上升沿,无延时’和‘上升沿、有延时’两种时钟工作模式。‘上升沿,无延时’模式与X5043的工作模式一致,数据在SPICLK信号的时钟上升边沿(从低电平到高电平)从移位寄存器移出在SI引脚上锁存,在时钟下降边沿(从高电平到低电平)从SO引脚上输出的数据锁存到移位寄存器中。‘上升沿,有延时’模式如图4所示,数据在SPICLK信号上升沿前半个周期从移位寄存器移出,在紧接着的上升边沿在SI引脚上锁存,在时钟下降边沿(从高电平到低电平)从SO引脚上输出的数据锁存到移位寄存器中。

3.2波特率的选择

SPI波特率可以由如下两种情况计算得出:

(1)对于SPIBRR=3~127,波特率的计算公式为:

SPI波特率=CLKOUT/(SPIBRR+1)

(2)对于SPIBRR=0~2,波特率的计算公式为:

SPI波特率=CLKOUT/4

式中,CLKOUT=器件的CPU时钟频率;SPIBRR=主SPI器件中的SPIBRR内容。</P>

X5043最大的SPI波特率为3.3MHz,若DSP的CPU时钟频率CLKOUT=16MHz,则:<BR>最大的SPI波特率 =16×106/(SPIBRR+1)≤3.3×106Hz<BR>SPIBRR≥4+9

3.3 DSP的数据传输格式

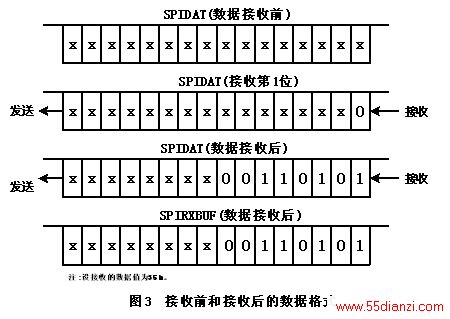

DSP中SPI有16位的发送和接收能力,且接收和发送均是双缓冲。所有数据寄存器都是16位宽的,而X5043的地址、数据寄存器均是8位的,将DSP中SPI传输字符长度设置成8位宽。要向X5043存储数据时,DSP将一个8位字节长度的数据写入SPIDAT或SPITXBUF的高8位上如图2所示,在时钟信号的作用下,以左对齐方式发送,先发送数据的最高位。DSP接收一个8位字节长度的数据,是以右对齐方式接收如图3所示,8位字节长度的数据写入SPIDAT或SPIRXBUF 的低8位上。

3.4各控制寄存器设置

<P>LDP #SPICCR>>7

SPLK #0007h,SPICCR

;复位SPI, 8个字符长度

SPLK #000Eh,SPICTL

;主模式,使能TALK,禁止SPI的中断<BR>;上升沿发送,下降沿接收,有延时SPLK #000Fh,SPIBRR;设置SPI的传输波特率

SPLK #0087h,SPICCR<BR>;SPI准备好发送或接收下一字符

3.5程序设计

RAM块中的变量定义:

.bss SPI_Xdata,1

;SPI数据传输暂存器

.bss address1,1

;EEPROM存储器地址暂存器

.bss data1,1<BR>;EEPROM存储器数据暂存器

X5043存储器地址:

WREN .set 0600h

;设置写使能锁存指令地址

WRDI .set 0400h

;复位写使能锁存指令地址

RSDR .set 0500h

;读状态寄存器指令地址

WRSR .set 0100h

;写状态寄存器指令地址

READh .set 0B00h

READl .set 0300h

;读存储器阵列数据指令地址

WRITEh .set 0A00h

WRITEl .set 0200h

;写存储器阵列数据指令地址

3.5.1 DSP的SPI数据发送、接收子程序代码

XMIT_value:

LDP #0

LACC SPI_Xdata

LDP #SPITXBUF>>7

SACL SPITXBUF

;写需发送的值到SPI传输缓冲器

XMIT_RDY:

LDP #SPISTS>>7

BIT SPISTS,BIT6

BCND XMIT_RDY,NTC

;测试SPI_INT位,如果SPI_INT=0,则重复循环

;等待数据发送完毕进行下一步操作

LDP #SPIRXBUF>>7<BR> LACL SPIRXBUF

;读取数据清除SPI_INT标志位

LDP #0<BR> SACL SPI_Xdata

;将接收的值存入数据传输暂存器

RET

3.5.2 X5043内部非易失性写判断子程序代码RSDR_WIP:

SPISTE_LOW

;置低SPISTE引脚,从而选通X5043

LDP #0

SPLK #RSDR,SPI_Xdata

CALL XMIT_value

;写读状态寄存器地址,高8位

SPISTE_HIGH

;置高SPISTE引脚,禁止X5043

LDP #0

BIT SPI_Xdata,BIT0

BCND RSDR_WIP,TC

;测试状态寄存器WIP位。如果WIP=1,正在进行内部写操作。

;等待内部写操作完成进行下一步操作

RET

使用上述判断子程序能够保证X5043完成内部写操作。向X5043存储器阵列写入数据时后面将跟随一次非易失性写操作。可以读状态寄存器检查WIP位,若WIP为高则非易失性写正在进行。X5043存储器非易失性写周期为10mS,也可以在一个写操作完成后作一个大于10mS的延时,以保证X5043完成内部写操作。

3.5.3向X5043 EEPROM存储器阵列中写数据

如图4所示,向EEPROM存储器阵列写入任何数据之前,必须用WREN指令设置WEL位。首先将CS拉低,向器件输入WREN指令,然后拉高/CS。再次拉低/CS并输入WRITE指令,紧跟随8位地址,然后是要写入的数据。WRITE指令的位3是地址位A8,该位选择阵列的高半部分或是低半部分。如果/CS在WREN和WRITE之间不变为高,则WRITE指令将被忽略。为了完成写操作,在最后一个被写入的数据字节的位0完成后/CS必须被拉高。如果它在任何其它时间被拉高,写操作将不完成。

本文关键字:暂无联系方式综合-其它,单片机-工控设备 - 综合-其它