串行器映射

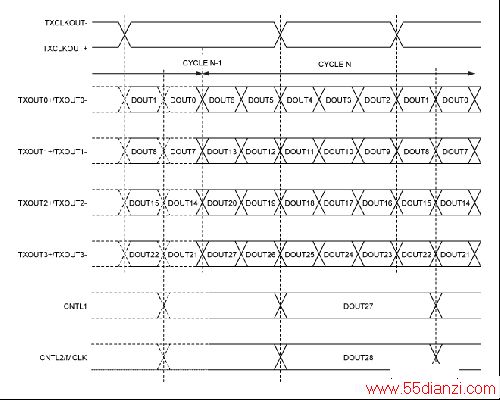

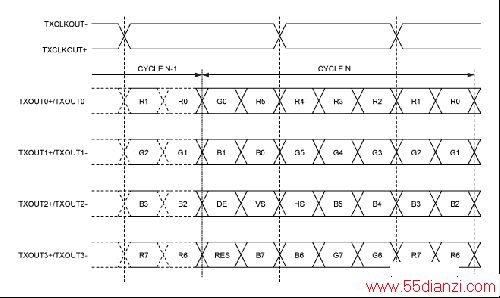

为匹配MAX9268解串器摄像链路的输出接口,并行RGB数据应按照以下信号图映射。图4所示为MAX9268并行位与其摄像链路输出之间的映射,图5所示为相机链路的RGB数据映射。表1所示为MAX9259串行器的对应内容映射。

图4. MAX9268内部并行至输出映射

图5. 摄像链路内容映射

表1. MAX9259串行器RGB内容位映射

DIN0DIN1DIN2DIN3DIN4DIN5DIN6DIN7DIN8DIN9

R0R1R2R3R4R5G0G1G2G3

DIN10DIN11DIN12DIN13DIN14DIN15DIN16DIN17DIN18DIN19

G4G5B0B1B2B3B4B5HREFVSYNC

DIN20DIN21DIN22DIN23DIN24DIN25DIN26DIN27DIN28

R6R7G6G7B6B7

色彩转换:YUV至RGB

FPGA芯片可将压缩(降低数据速率)后的摄像头数据YUV转换成RGB数据,用于MAX9259串行器。采用8位定点运算时,色彩空间转换的公式如下,式2和式3中,Dn和En的n为偶数。

Cn = Yn - 16

Dn = Dn + 1 = Un - 128

En = En + 1 = Vn + 1 - 128

Rn = clip((298 × Cn + 409 × En + 128) >> 8)

Gn = clip((298 × Cn - 100 × Dn - 208 × En + 128) >> 8)

Bn = clip((298 × Cn × 516 × Dn + 128) >> 8)

式中,>> 8表示“向右移8位”,clip表示“只取最低8位”。

FPGA方案

输入缓冲

输入缓冲电路包括计数器、三个寄存器和组合逻辑,将单字节时钟输入转换成三字节时钟输出,输出时钟速率为输入的一半。组合逻辑仅用于分别使能Y、U和V字节的对应寄存器。

图6. 输入缓冲电路

时钟开关

FPGA输出像素时钟速率为摄像头像素时钟的一半,用于驱动串行器像素时钟输入。但是,摄像头在初始化之前不会输出像素时钟。解决方案是在FPGA内部采用2:1时钟复用器(mux)和时钟信号检测器,mux由时钟信号检测器控制。上电时,mux的默认时钟来自摄像头的时钟振荡器,使SerDes芯片组提供启动摄像头的控制通道。时钟信号检测器对场同步信号脉冲进行计数,经过几个场同步脉冲后,mux切换到摄像头像素时钟速率的一半。采用高清摄像头传感器时,例如OV10630,每个场同步周期包含100k以上的像素时钟。几个场同步周期足以使摄像头的锁相环(PLL)达到稳定。场同步计数比像素时钟计数的效率高得多,并可节省FPGA逻辑单元的资源。

中间缓冲

格式转换表达式中没有体现硬件电路的延迟。为了从YUV输入生成RGB数据,需要两到三次乘法运算和三到四次加法运算。尽管FPGA逻辑电路(门电路) 的延时只有几个纳秒,但载波传输、加法器、移位乘法器都会导致不同程度的延时,使整体延时增大。为了使延迟最小化,每个常数乘法器均由两个移位输入(代表常数的2个非零最高有效位MSB)的加法器近似。输入的YUV字节速率大约为100MHz时,延迟会跨越相邻像素的定时边界,增大图像噪声。在每个乘法器之后通过中间寄存器来消除扩展延时。

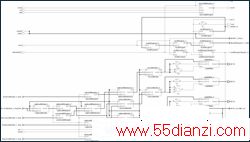

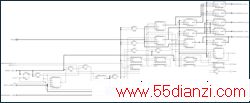

以上提及的YUV至RGB彩色转换已用于Actel® ProASIC3 A3PN125Z FPGA,图7所示为实现这一FPGA的原理图。

清晰图像(PDF, 172kB)清晰图像(PDF, 180kB)

图7. YUV至RGB转换器的FPGA实现