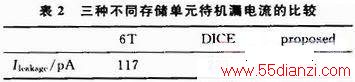

在亚阈值电压下工作的电路设计中,尤其对于存储器的设计,待机漏电功耗占据了所有功耗的主要部分。表2是在0.3 V的电压下,三种不同的存储单元即常规的6T单元,常规DICE单元,本文提出的存储单元之间待机漏电流的比较。

从表2可以看出,常规DICE单元漏电流是6T单元漏电流的2倍,本文设计的基于DICE结构的存储单元的漏电流略高于常规DICE单元的漏电流,使其功耗也略高于常规DICE单元的功耗,但是这对于电路的稳定性是有意义的。

图6显示了SRAM的仿真波形,从波形可以看出,采用本文设计的存储单元结构,该SRAM具有稳定的数据输出,从而保证了SRAM工作的稳定性,同时该结构可以有效地防止单粒子翻转效应。

4 结语

本文介绍了由16个晶体管组成的存储单元,这种基于DICE结构的SRAM存储单元与许多常规的存储单元相比,提高了电路的稳定性和可靠性。因其工作在亚阈值电压下,漏电流和功耗相对于常规的DICE存储单元稍大一些,但它能够在读取数据过程中有效地防止单粒子效应对电路的影响。本文提出的存储单元是为了工作在亚阈值电压下,此时存储单元的漏电流远远比工作在标准电压下的漏电流低得多,所以这种存储单元对于低功耗、高稳定性电路具有广泛的应用前景,例如在空间技术应用、电路通信、生物医学以及军事应用领域中。

本文关键字:存储器 综合-其它,单片机-工控设备 - 综合-其它