目前,DSP技术已广泛用于信号处理、通信和雷达等领域。TI公司的带EMIF扩展存储器接口的浮点DSPTMS320C672x系列是专为高速、高性能应用而开发的,主要应用于高速宽带、图像处理和高速铁路轨道信号处理等领域。DSP应用平台设计中,外部存储器接口(EMIF)是为DSP与外部设备之间提供连接。EMIF和外部器件SDRAM以及Flash的合理设计关系到系统的数据存储和程序加载。

TMS320C672x系列浮点DSP的EMIF性能优良,增强了与外部1、2或4区的16位或32位SDRAM和异步器件连接的方便性和灵活性。TMS320C6722和TMS320C6726 EMIF宽度为16位,支持的SDRAM可达128 Mb;TMS320C6727EMIF宽度为32位,支持高达256Mb和512Mb的SDRAM。

异步存储器接口是从并行的8位、16位或32位NOR Flash实现系统自启动。若使用大容量的Flash,EMIF连接Flash的高位地址线可通过外部器件CPLD或自身GPIO口扩展。

1 EMIF接口

EMIF接口具有很强的外设连接能力,可寻址空间一般比较大,数据吞吐较快。EMW接口支持的器件包括同步突发静态RAM(SBSRAM)、同步动态RAM(SDRAM)、各种异步设备(SRAM、ROM和FIFO)以及同步FIFO。TMS320C672x的EMIF引脚结构如图1所示。

其主要引脚功能如下:

EM_A[x:0]:EMIF地址总线。当与SDRAM器件连接时,地址总线主要为SDRAM提供行地址和列地址。当与异步器件连接时,这些引脚与EM_BA引脚提供器件地址。

EM_BA[1:0]:EMIF存储区地址线。与SDRAM连接时,为SDRAM提供存储区地址。与异步器件连接时,这些引脚与EM_A引脚共同提供器件地址。

EM_WE_DQM[x:0]:低电平有效写触发或字节使能引脚。与SDRAM连接时,这些引脚与SDRAM的DQM引脚连接。在数据访问中分别使能/禁止每一字节。与异步器件连接时,这些引脚可作为字节使能(DQM)或字节写触发(WE)。

EM_CS[0]和[2]:CS[0]为SDRAM器件低电平有效芯片使能引脚,当访问异步器件时此引脚失效,在完成异步存取后自动恢复其功能;CS[2]为低电平有效异步器件使能引脚,仅在访问异步存储器时有效。

EM_RAS:低电平有效行地址选通引脚,与SDRAM的RAS引脚连接,用于向此器件发送命令。

EM_CAS:低电平有效列地址选通引脚,与SDRAM的CAS引脚连接,用于向此器件发送命令。

EM_CKE:时钟使能引脚,与SDRAM的CKE连接,发出自刷新命令,使器件进入自刷新模式。

EM_CLK:SDRAM时钟引脚,EMIF时钟来自DSP的PLL控制器的SYSCLK3时钟模块。

2 EMIF与SDRAM的设计

这里以SDRAM(HY57V281620A)为例,说明EMIF和SDRAM的接口与配置,HY57V281620A是4 Bankx2MBx16 bit的SDRAM器件,可与TMS320C67 22 DSP无缝连接。图2是TMS320C6722型DSP与HY57V281620A型SDRAM的电路连接。

2.1 SDRAM的软件配置

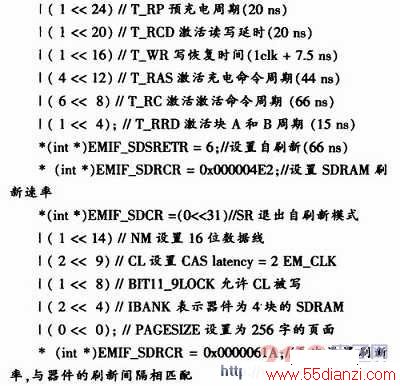

在TMS320C6722的EMIF中有一组存储器映射寄存器,通过设置这些寄存器便可完成对SDRAM的配置,包括配置寄存器SDCR、刷新控制寄存器SDRCR、时序寄存器SDTIMR和自刷新退出时序寄存器SDSRETR。具体的配置代码如下:

![]()

2.2 SDRAM的软件操作

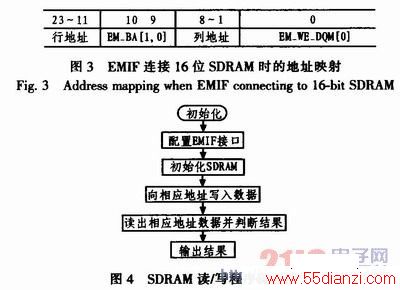

根据上面软件配置中IBANK和PAGESIZE字段的设置,图3列出了C6722 EMIF连接16位4区256字页面的SDRAM地址映射关系,其他系列地址映射关系参考TI资料。SDRAM读/写程序流程如图4所示。

www.55dianzi.com

EMIF控制SDRAM工作时,当行地址选通引脚EM_RAS有效时,SDRAM通过A0~A11获取行地址;当列选通引脚EM_CAS有效时,SDRAM通过A0~A11获取列地址。EMIF访问的外部SDRAM空间地址映射为0x80000000-0x8FFFFFFF,由表1的地址映射知,如果要存储16位的short int型数据到SDRAM,每次逻辑地址需要加2,如:*(short int*)(0x80000000+i*2)=short int i;存储32位的int型数据每次地址需要加4,如:*(int*)(0x80000000+i*4)=int i。

3 EMIF与Flash的设计

当DSP脱机运行时,系统上电或复位后,DSP系统自带的Bootloader将一段存储在外部的非易失性存储器中的代码搬移到内部高速存储单元中执行。这样既利用了外部存储单元扩展DSP本身有限的ROM资源,又充分发挥了DSP内部资源的效能。TMS320C672x系列DSP只支持一种硬启动选项,即从内部ROM地址0x00000000启动,其他启动选项由存储于ROM的软启动器实现。软启动器使用CFGPIN0和CFGPIN1寄存器,这2个寄存器在复位时捕捉相关器件引脚的状态,以决定进入那种启动模式。ROM主要有4种自启动模式:从EM_CS2空间的并行Flash启动、利用SPI0或I2C1主模式从EEPROM启动、利用SPI0或I2C1从模式从外部MCU启动以及利用UHPI口从外部MCU启动。这里分析了从EM_CS2空间的并行Flash启动模式,给出了高密度、非易失性的电可擦除存储器AM29LV800BB-90EC(512 Kx16 Bit)与EMIF的接口设计方案。

3.1 Flash的硬件连接

AM29LV800BB~90EC型Flash具有19根地址线,而TMS320C6722 EMIF只有14根地址线(EBA0~EBA1、EA0~EA11)。因此,EMIF与Flash连接时地址线不够用,需要扩展高位地址线,这里提出两种扩展方法:GPIO扩展和CPLD地址锁存器扩展。

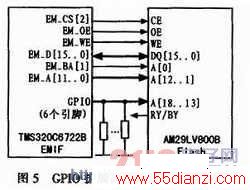

3.1.1 GPIO扩展

TMS320C672X MCASP通道的各功能引脚都可以作为通用的I/O接口,直接与Flash存储器的高位地址线连接。硬件原理图如图5所示研。图5中,任何在复位时可下拉的GPIO引脚都可用于控制Flash启动器的地址线A[18:13]。

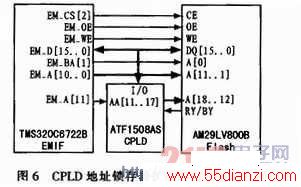

3.1.2 CPLD地址锁存器扩展

在CPID中设计一个地址锁存器74L273,通过74L273的输出口扩展7根高位地址线A11~A17,分别与Flash的A12~A18连接。EMW的EM_A[11]作为CPLD锁存器的输入选通端选,EMIT数据线作为锁存器的输入,如图6所示。

3.2 FLash的软件配置

在EMIF异步接口中,AICR是唯一需要编程的寄存器。根据Flash器件的特性,配置如下:

3.3 Flash的软件操作

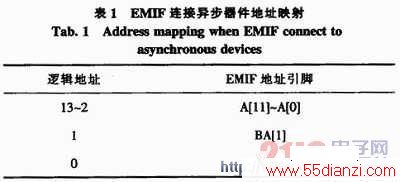

TMS320C672x DSP的存储器中EMIF访问的外部异步器件Flash空间地址映射为0x90000000~0x9FFFFFFF之间。由于Flash数据总线宽度为16位,因此在硬件设计时选用半字寻址,即EMIF的BA[1]连接Flash的A[0]。根据配置寄存器A1CR中数据总线宽度的配置,访问异步器件时TMS320C6722中内部地址和EMIF地址引脚对应如表1所示。

www.55dianzi.com

Flash在读操作中类似于普通的ROM,在写操作中需要使用一些特殊命令字,按一定的顺序编程,且可随时编程,编程命令根据器件参考资料。对Flash的读/写流程如图7所示。

本文关键字:暂无联系方式嵌入式系统-技术,单片机-工控设备 - 嵌入式系统-技术