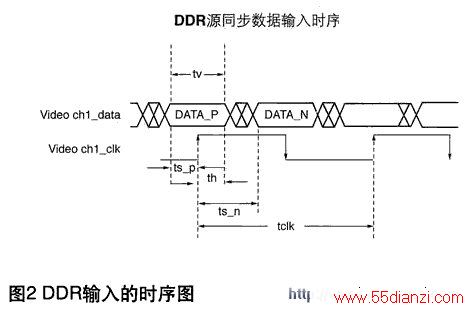

对于源同步数据,在SDR的情况下,我们可以将输入时钟设置为0度相移或180度相移,而在DDR的情况下可以将其设置为90度相移。图2所示为时钟在90度相移时的源同步DDR数据输入时序。

对于PCIExpress核和千兆位以太网MAC核上的时序约束,我们按照CORE Generator示例中的定义对BLOCk RAM和PLL/DCM使用了所有时序和布局约束。

因为许多Virtex-5设计都使用多个异步时钟,所以我们必须在设计中定义伪通路,以使这些时钟不受影响。

布局布线后的时序分析和时序校正

对设计进行布局布线后,我们运行了静态时序分析(STA)和时序仿真,以了解是否存在其他时序错误。对于STA,我们确保时序报告涵盖了有约束和无约束的全部通路。通过使用STA报告,我们可以鉴定输入/输出时序和内部系统时序。

事实证明,基于Virtex—5的FPGA非常适合我们的视频监视系统的要求。区域时钟缓冲器和I/O时钟缓冲器使我们能够支持多信道源同步音视频输入。而且,该器件的PCI Express和千兆位以太网MAc硬宏为我们提供了进行远程监视所需的全球连接能力。

在未来的设计工作中,我们将可依靠前期规划来确保有效使用特定FPGA的可用资源,设计出具有附加价值的产品。

本文关键字:暂无联系方式嵌入式系统-技术,单片机-工控设备 - 嵌入式系统-技术

上一篇:正交相干检波方法及FPGA的实现