引 言

随着 嵌入式系统 应用的迅速发展,PDA和移动电话等便携式装置深入到生产生活的各个角落,嵌入式系统市场有迅速增长趋势。嵌入式系统一般是由电池来供给电能的,而且大多数嵌入式设备都有体积和重量的约束。减少电能消耗不仅能延长电池的寿命,缩短用户更换电池的周期,而且能提高系统性能与减小系统开销,甚至能起到保护环境的作用。

1 嵌入式系统 功耗 分析

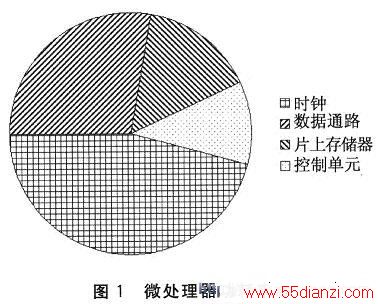

研究微处理器的低功耗设计技术,首先必须了解它的功耗来源。如图1所示,从高层次 仿真 得出的结论可以看出,通过开关级功率模拟所获得的高性能 CPU 的功率分布关系。其中,时钟功耗所占比例最大,包括时钟发生、驱动器、时钟树、锁存器和所有时钟负担的器件;数据通路的功耗仅次于时钟,主要包括执行单元、总线和寄存器文件;片上存储器的功耗主要由存储器的大小以及存储阵列的电路和物理结构所决定;控制单元和I/O的功耗通常占整个芯片功耗的一小部分。

2 嵌入式系统低功耗设计

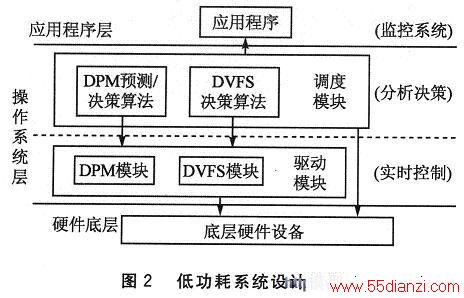

低功耗设计是一个复杂的综合性课题。就流程而言,包括功耗建模、评估以及优化等;就设计抽象层次而言,包括自硬件底层至应用程序层的所有抽象层次,而目前低功耗设计大都在操作系统层实施,如图2所示。同时,功耗优化与系统速度和面积等指标的优化密切相关,需要折中考虑。下面根据各部分在嵌入式系统中的不同层次,讨论常用的低功耗设计技术及具体应用。

2.1 低功耗硬件设计

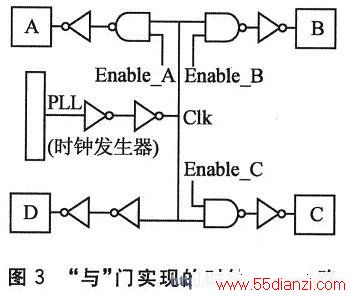

低功耗硬件设计是嵌入式系统降低功耗的重要内容。因此,需要从系统内部结构设计、系统时钟设计和低功耗模式等几方面采用特定的方法(例如,门控时钟和可变频率时钟、并行结构与流水线技术、低功耗单元库、低功耗状态机编码、Cache低功耗设计等)来实现系统硬件节能设计。下面介绍门控时钟和可变频率时钟的应用。时钟是惟一在所有时间都充放电的信号,而且很多情况下引起不必要的门的翻转,因此降低时钟的开关活动性将对降低整个系统的功耗产生很大的影响。门控时钟包括门控逻辑模块时钟和门控寄存器时钟。门控逻辑模块时钟对时钟网络进行划分,如果在当前的时钟周期内,系统没有用到某些逻辑模块,则暂时切断这些模块的时钟信号,从而显著降低开关功耗。图3为采用“与”门实现的时钟控制电路。门控寄存器时钟的原理是当寄存器保持数据时,关闭寄存器时钟,以降低功耗。门控时钟易引起毛刺,必须对信号的时序加以严格限制,并对其进行仔细的时序验证。

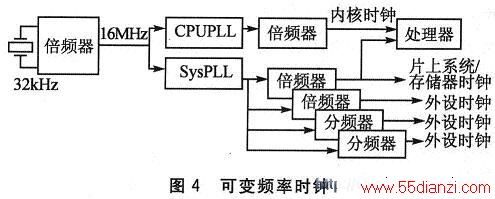

另一种常用的时钟技术就是可变频率时钟。它可根据系统性能要求,配置适当的时钟频率以避免不必要的功耗。门控时钟实际上是可变频率时钟的一种极限情况(即只有0和最高频率两种值),因此,可变频率时钟比门控时钟技术更加有效,但需要系统内嵌时钟产生模块PLL,增加了设计复杂度。图4为在具有低功耗特性的嵌入式芯片上进行的时钟系统设计方案。片上时钟系统通过2个数字锁相环CPUPLL和SysPLL来稳定16 MHz的输入时钟,分别送到不同的倍频器和分频器。经CPU-PLL的时钟信号作为处理器内核时钟,经SysPLL的时钟信号作为处理器内核之外的系统时钟、存储器时钟和外设时钟。

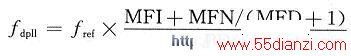

由于处理器芯片(如i.MX1)不支持电压动态调节,可通过配置片内数字锁相环实现内核频率动态调节。根据公式计算出系统频率:

其中:fref是系统的低频时钟频率,作为倍频的参考频率;MFI是倍频因子的整数部分;MFN和MFD分别是倍频因子的分子和分母;PD是预设分频因子。

2.2 操作系统层

系统级低功耗设计一般是在操作系统层实现。因为操作系统管理系统所有软硬件资源,并获取系统的各种状态信息,控制硬件设备的状态。因此,在操作系统中实现全局功耗控制是最佳选择。操作系统层面分成功耗驱动模块和功耗调度模块。

2.2.1 功耗驱动模块

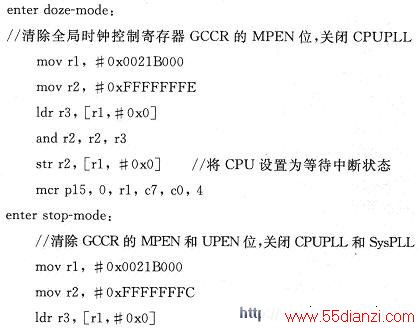

驱动模块实现相对简单,主要是对硬件操作。功耗模式转换和频率调节都是通过片上时钟系统控制寄存器进行设置。因此,实质上是对寄存器的设置。从睡眠模式或停止模式进入运行模式相对容易,只需向系统发出中断信号,唤醒系统进入运行模式。而从运行模式到睡眠模式或停止模式相对复杂,其关键代码如下:

2.2.2 功耗 调度模块

功耗调度模块实现的关键技术在嵌入式Linux操作系统中有具体体现。在Linux操作系统中,任务的调度主要由进程调度(或任务调度)模块 schedule()完成。schedule()掌握系统内所有进程的运行状态,并对其执行的优先级进行管理调度。因此,系统级实现功耗控制,需要对嵌入式Linux内核的schedule()模块全面改写,将 DPM 和DVS策略加入其中。设计思路为:由于Linux内核提供的 CPU _usage_stat结构记录了处理器运行时间的分配情况,可以通过读取这些参数计算出当前系统的运行比例,即通过cpu_sCAN函数来实现具体的操作。cpu_scan函数是处理器设备驱动的主要部分,它在固定的时间片内调用,时间片的大小可以根据需要在5~1D0 ms之间选取。该函数通过调用cpu_dvs函数和cpu_dmp函数来评估系统的状态,这两个函数分别是可变电压技术和动态功耗管理的实现。

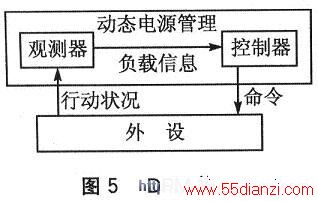

(1)DPM策略

DPM策略在低功耗嵌入式Linux系统的实现上分为观测器和控制器两部分,如图5所示。我们在实现过程中采用了Timeout算法。该算法实现简单,预测准确性也较高。统计表明,只要合理地设计Timeout,这种假设的可信度为95%。采用了Timeout算法的cpu_dmp函数在此不再具体解释。但在动态电源管理实现过程中容易出现一个唤醒信号发送给一个等待队列中的进程后,该进程不能够立即被调度执行,从而造成事件丢失的情况。为了避免这种情况的出现,Llow被设置成比Lmax稍小的值。当事件数量到达Llow时,即使事件处理进程被唤醒后不能马上转入执行,由于Llow<Lmax,事件列表还没有全满,也不会造成新事件丢失。这样,既降低了事件丢失的几率,对系统的影响也降到了最小,因为只有当事件列表快满时才会调用事件处理进程。

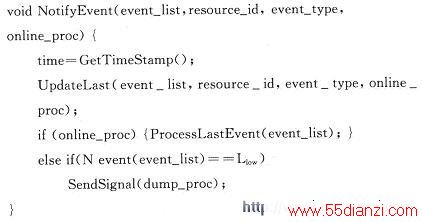

更新事件列表算法代码如下:

显式资源需要对驱动程序作一些修改,即在驱动程序发送执行命令前和硬件完成服务并通过驱动程序告诉内核设备就绪后这两个时间点,插入一个NotifyEvent()函数调用。具体的代码插入点根据不同类型的设备和对服务开始与结束的不同定义而不同。

根据观测器得到的系统资源访问历史记录计算出优化策略之后,控制模块将在通过电源管理机发出控制命令给相应的硬件完成服务,并通过驱动程序告诉内核设备就绪后这两个时间点插入一个NotifyEvent()函数调用。

(2)DVS策略

目前, 嵌入式系统 降低功耗多采用动态电压缩放技术Ⅲ,即系统运行时可以通过设置可编频率寄存器控制处理器的工作频率。实验观察发现,系统的运行负荷具有明显的非平稳特性,短时间内可能具有很高的执行负荷,但绝大部分时间维持轻负荷状态。DVS技术根据嵌入式系统这一特点,在系统负荷较重时将处理器设置为最高执行速度,以保证系统的计算能力;而在系统负荷较轻时动态降低处理器的工作频率,以降低处理器的执行功耗,从而实现系统计算性能与功耗的优化控制,如图 6所示。DVS的预测通过采用了基于时间间隔AVGn算法的cpu_dvs函数实现。该函数读取CPU使用信息,按照AVGn算法来估算系统的运行负荷,并根据返回给cpu_scan函数的结果实现具体的动态电压缩放。

本文关键字:嵌入式 嵌入式系统-技术,单片机-工控设备 - 嵌入式系统-技术