��������

����Ƕ��ʽʵʱ����ϵͳ�� RTOS ,Real Time Operating System��ΪǶ��ʽӦ�õĿ������ṩ��ϵͳ����֧�Ż���������ؼ���Ƕ��ʽ����ϵͳ����ƹ��̣���Ϊ����ϵͳ��һ���dz���Ҫ�ķ�֧������RTOS��Ƕ��ʽϵͳ�еĴ���Ӧ�ã�RTOS��ѡ�������۳�Ϊ��һ����Ҫ�����⡣һ��RTOS������Ҫ�Ӻܶ�ǶȽ��У�����ϵ�ṹ��API�ķḻ�̶ȡ�����֧�֡��ɿ��Եȡ����У� ʵʱ�� ��RTOS���۵�����Ҫ��ָ��֮һ��ʵʱ�Ե��������û�ѡ�����ϵͳ��һ����Ҫ�ο�������һ������ϵͳ��ʵʱ��Ӧ�����ؿ���������Щָ�꣬�Լ���ν��в��ԣ��DZ����������۵����⡣

����1 ����ϵͳʵʱ�Ե���Ҫָ��

�����ϸ��˵��Ӱ��Ƕ��ʽ����ϵͳʵʱ�Ե������кܶࡣ����ƪ��������ֻ�г�Ӱ�����ϵͳʵʱ�Ե�6����Ҫ���ء�

������1������ϵͳ����ƽ������ʱ��

������ϵͳ����Ч�ʣ���ָ�ں�ִ�г��õ�ϵͳ���������ƽ��ʱ�䡣���Բο�POSIX�������ս��̡��̡߳�ͬ��ԭ��ź����ͻ�����ȣ����ļ����ڴ桢�жϴ�����ʱ�ӡ�ʱ����࣬ѡȡ���ֳ��õ�ϵͳ���ý��в��ԣ��罨��/ɾ���������̡߳�����/ɾ���ļ�����/д�ļ�������/�õ����ȼ�������/�ͷ��ź���������/�ͷ��ڴ�ռ䡢����/ж���жϴ���ģ��ȡ�ѡȡ������������ʮ��������������ֻ����Ϊһ�ַ�������������ο���

������2�������л�ʱ��

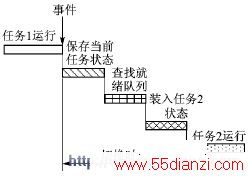

���������л�ʱ����ָ�¼������л��ӵ�ǰ����ֹͣ���С���������״̬��CPU�Ĵ������ݣ�����װ����һ����Ҫ���е�����״̬����ʼ���е�ʱ��������ͼ1��ʾ��

ͼ1 �����л�ʱ��

������Ҫע����ǣ�Ҫʹ��������л�����Ҫһ�����¼�������ͨ��������¼���ͬ��ԭ�ʹ�����л������ҹ��̿ɱ���ء����ǣ�ͬ��ԭ��IJ��������һ����ϵͳ���������Ҳ�ͬ����ϵͳ�ĸ���ͬ��ԭ�����Ч�ʲ�ͬ����ˣ��Ա������ϵͳʹ����֧�ֵĸ���ͬ��ԭ����������л����ԣ�ѡȡ������ʱ�����ߡ��������Ϊ�����ԭ�����Ϊ����ֵ����ʹ�����С��������Mutex��Semaphore��CritICal Section��SVR5 Semaphore��POSIX Semaphore��pthread_mutex�IJ���֮���WinCE�����ԭ��ΪCritical Section����Linux�����ԭ��Ϊpthread_mutex��

������3���߳��л�ʱ��

�����߳��ǿɱ����ȵ���С��λ����Ƕ��ʽϵͳ��Ӧ��ϵͳ�У��ܶ�������̵߳ķ�ʽִ�еģ������߳��л�ʱ��ͬ���ǿ����һ��Ҫ�㡣���Է�����ԭ���������л����ƣ����ٽ��ܡ�

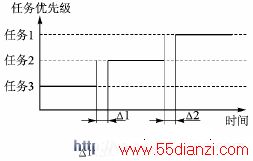

������4��������ռʱ��

����������ռʱ���Ǹ����ȼ���������������еĵ����ȼ������л��ϵͳ����Ȩ�����ĵ�ʱ�䣬��ͼ2��ʾ��

ͼ2 ������ռʱ��

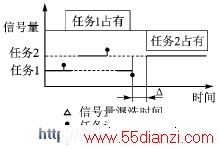

������5���ź�����ϴʱ��

�����ź�����ϴʱ��ָ��һ�������ͷ��ź�������һ���ȴ����ź������������ʱ���ӳ٣���ͼ3��ʾ��

ͼ3 �ź�����ϴʱ��

������Ƕ��ʽϵͳ�У�ͨ������������ͬʱ����ijһ������Դ�������ź����Ļ�����ʱ�֤����һʱ��ֻ��һ�������ܹ����ʹ�����Դ���ź�����ϴʱ�䷴ӳ���뻥���йص�ʱ�俪������RTOSʵʱ�Ե�һ����Ҫָ�ꡣ

������6���ж���Ӧʱ��

�����ж���Ӧʱ����ָ���жϷ�������ʼִ���û����жϷ������������������жϵ�ʱ�䡣�жϴ���ʱ��ͨ��������RTOS���������һ����û����жϴ���������������Բ�Ӧ�����ڲ��Կ��֮�ڡ�

���������Щָ��IJ��ֻ�ȫ�����Ѿ�����Ϊ�����ٵIJ��Է����Ͳ��Գ�������Rhealstone������������benchmark��lmbench��HbenchOS�ȣ�������Щ���Է�����������������ڼ�ʱ�����IJ��㵼�¼�ʱ���Ȳ�����������������Ҫ�����רҵӲ���豸�����������ǡ�ʾ�������ȣ���ʹ�ò���Ҫ����ߣ������������״ﵽ����������һ����ȱ�ݡ������Щ���⣬�����������һ�ֻ���CPLD��Ŀ��ϵͳ��ϵIJ��Է������Ϻõؽ������Щ���⡣

����2 �ȶ�ƽ̨�����Է���

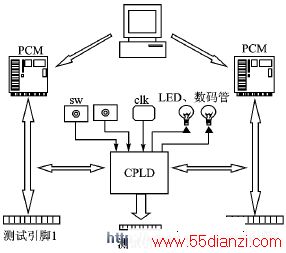

����2.1 �ȶԲ���ƽ̨����

����Ϊ�˸��õض�Ƕ��ʽϵͳ�и���ε�����ϵͳ����������ϵͳ��Bootloader���û�Ӧ�ó����Լ�����ϵͳ���������⣬������Ʋ�ʵ����˫Ƕ��ʽϵͳ �ȶ�ʵ��ƽ̨ ��ʵ��ƽ̨��2���л�PCM7230�����壨����PXA255����������1��CPLD����Ϊ���ģ������������б������ϵͳ����֤�˲��Ի�������ȫ��ͬ��CPLD������������жϸ��ء�˫ϵͳ��ͬ����λ/��λ�������ʱ���ܣ���֤�˲��Խ���ľ�ȷ���������ڱȶԡ��۲죬ͻ��������̱ȶԵ��ص㡣ͼ4�DZȶԲ���ƽ̨�����ṹ��

ͼ4 �ȶԲ���ƽ̨�����ṹ

���������г����DZȶ�ƽ̨����Ҫ��Ӳ���ͺ������ࡣ

����2.2 �������ʱ����

�����ڲ��Թ����У����õ�ǰ�Ƚ����еĻ����Գ���benchmark�������� ʵʱ�� ָ��������⡣���ÿһָ�꣬��д��Ӧ�IJ��Գ����ڲ��Թ����У�һ�������ԭ���Ǿ����ܵؼ�С���������ö��ֲ��Լ�С�������ضԲ��Ե�Ӱ�죬����ر��ں��в��ֲ���Ҫ�Ľ��̣��������ں�ռ��CPUʱ�䣻��������Cache��ָ��Cache���Ա�����ٻ���� RTOS ��Ӧָ���Ӱ�죻��ͬһָ����и�Ƶ���ظ����ԣ�ͳ�������ֵ����Сֵ��ƽ��ֵ�ȣ��õ������ܿ۵Ľ����

������ͨ���Ļ����Է�����Ƚϣ������Է������ص��Dz���CPLD��������Գ������ϵķ���������CPLD�뿪�����Ϸḻ��������Դ��ͨ��CPLD���б�̣��ɷ���ضԱ�����ϵͳ�����жϸ��ء�ͬ�����������Ҳ������ӱ���ϵͳ�Ķ��⸺�ء�ͬʱ������ϵͳ���õĴ�����ʹ���Խ�����Ӿ�ȷ�����ӽ��ں�����������ֵ��

�������⣬���Թ��̵ļ�ʱ����ͨ��CPLD���ʵ�֣��봫ͳ������RTOS�ں˵�ʱ��ϵͳ���ü�ʱ��ʽ��ȣ�����˲�ͬ����ϵͳϵͳ���÷���ֵ���Ȳ�������λ��ͳһ�����⡣���ڱȶ�ƽ̨�е�CPLD����ѡ�õ���Xilinx��˾��XC9500ϵ�У������ϵͳʱ��Ƶ��Ϊ100MHz�����ŵ����ŵ����ʱ��Ϊ10 ns�����ʵ�ֵļ�������ʱ���ȿ��Դﵽ��ʮns���������Ժ��Բ��ƣ���������˼�ʱ���ȣ���ͼ5��ʾ��

ͼ5 CPLD���ԡ���ʱ����

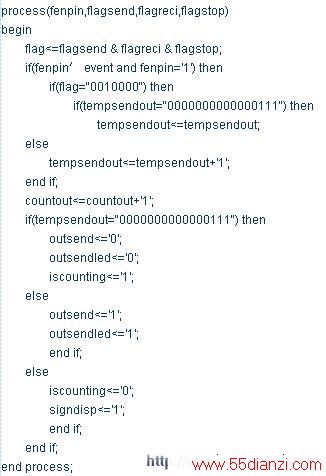

�����������Թ�����Ҫ��Ϊ4���֣����������ں˲��Գ����̣�CPLD��̣�����罻�����ֵ�ʵ�֡����������������ںˡ���Bootloader�ȣ�Bootloaderͨ����i�Mboot�Mlite�M1.8�����ģ�ʹ���Ӧ���ڱȶ�ƽ̨�ϣ��ں˲��Գ�����ǰ�����ᵽ��6��ָ�꣬����Ϊ6��ģ�飬�ֱ��д��CPLD�����Ҫ������ʱ�����жϸ��ؼ��س���ȣ���罻��������Ҫ��������ͨ�š���̫���������������Dz���CPLD�ϵ�VHDL����Դ�롣���У�fenPINΪʱ��Ƶ�ʣ�flagreciΪ�����źţ���ʹ�ð����˹�����ʱ��flagsend��flagstopΪ��ʱ��ʼ�ͽ�����

�������Գ���Ĵ���϶࣬���ﲻһһ�г���������������Ƕ�����CPLD�����IJ��ִ���Ƭ�ι��ο���

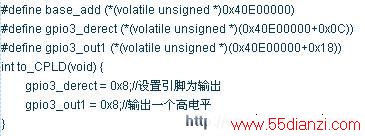

���������ǰ�ζ�������ؼĴ����ĵ�ַ���ڲ��Թ����У�ʹ��PXA255��GPIO3������CPLD������ʵ�ּ�ʱ���ܡ�������Ҫ���ں�̬���У��ʸú�����Ϊһ��ģ�������ںˣ����Գ�����ͨ��ioctlϵͳ����ִ�д˶δ��룬���źŷ���CPLD��CPLD����2���źŵļ��ʱ�䣬ʵ�ּ�ʱ���ܡ�

���Ĺؼ��֣�Ƕ��ʽ ����ϵͳ Ƕ��ʽϵͳ-��������Ƭ��-�����豸 - Ƕ��ʽϵͳ-����