引 言

嵌入式 实时系统要求系统有很好的实时性,能够及时处理各种异常事件,因此 中断系统 是嵌入式实时系统的重要组成部分,其时间和空间性能对嵌入式实时系统性能的影响至关重要。要想缩短嵌入式实时系统的中断响应时间并提高系统中断处理效率,合理地设计中断系统非常关键。S3C44BOX是三星公司基于 ARM 7TDMI内核的微处理器,支持IRQ和FIQ中断请求,同时还支持向量中断,以缩短中断响应时间。嵌入式实时操作系统μC/OS-II提供了简单的中断管理机制对系统中断进行统一管理,但是对于不同的微处理器没有给出具体的中断处理方法。本文在深入分析S3C448OX中断控制系统和μC/OS-II中断管理机制的基础上,进行中断系统设计,使之能更好地满足实际应用的需求。

1 S3C4480X 中断系统

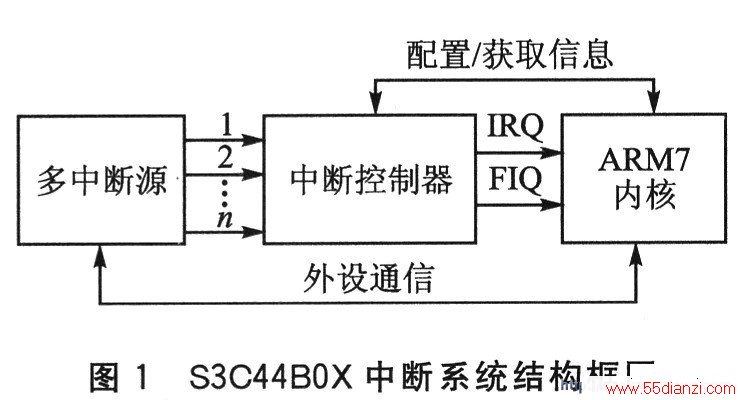

图1所示为S3C44BOX的中断系统结构框图。中断控制器的任务是在片内外围和片外中断源组成的多重中断发生时,经过优先级判断、选择其中一个中断;通过IRQ或FIQ向ARM7内核发出IRQ或FIQ中断请求,ARM7内核从中断控制器中获取中断信息,然后对中断进行处理,控制中断设备的操作过程。

点击看原图

当ARM7内核接收到中断控制器的中断请求时会自动执行以下几步操作,以实现中断环境保护和程序跳转:

①将程序状态寄存器CPSR的内容保存到将要执行的中断模式的程序状态保存寄存器SPSR中,以实现对处理器当前状态、中断屏蔽位和各条件标志位的保存。

②设置当前CPSR中的相应位,屏蔽相应中断并切换处理器模式。

③将引起中断指令的下一条指令的地址(断点地址)保存到中断模式的子程序链接寄存器LR中,使中断服务程序执行完后能正确返回原程序。

④给程序计数器PC强制赋值,使程序从相应的向量地址开始执行中断服务程序。

当中断服务程序执行完后,需要执行以下几步操作从中断服务程序中返回:

①从中断模式堆栈中恢复所有修改过的通用寄存器(RO~R12)。

②将中断模式SPSR寄存器的内容复制到CPSR中,恢复被中断模式程序的工作状态。

③将LR的内容赋给PC,使PC返回到相应的指令处。

④清除CPSR中的中断禁止标志位。

在中断返回的过程中,②和③需要同时完成。

2 μC/OS-II中断处理过程

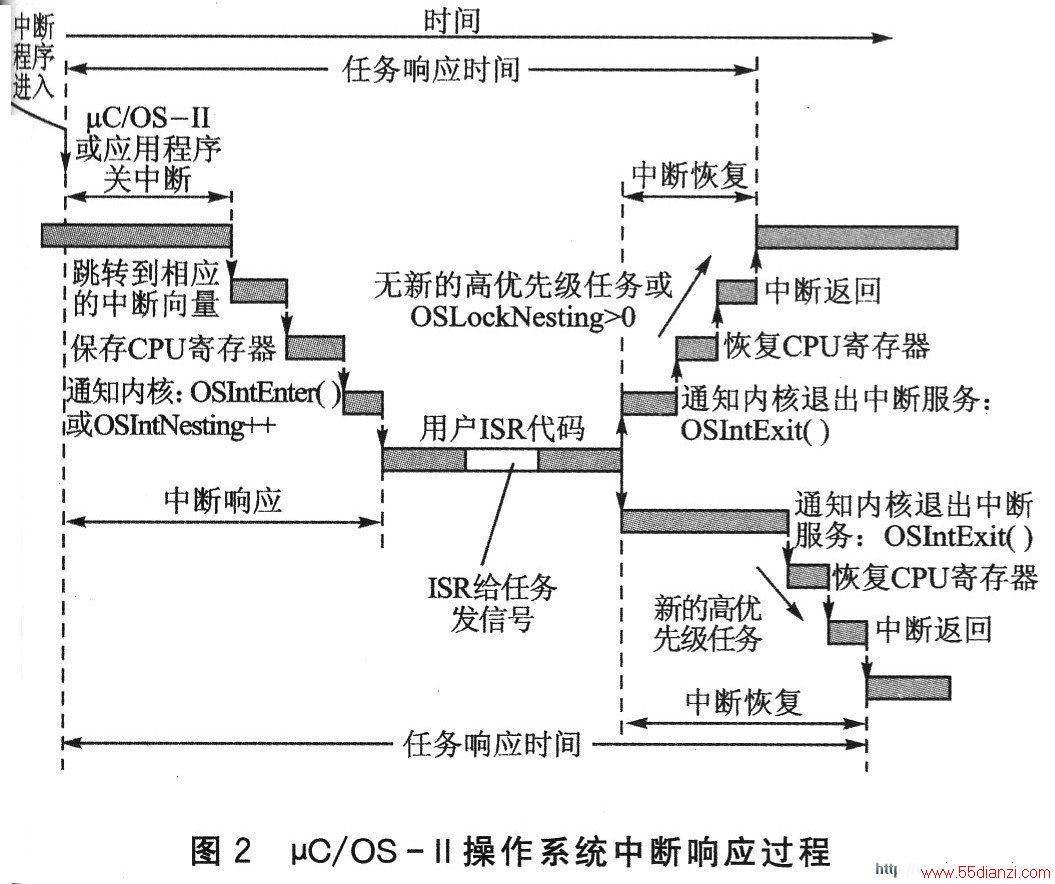

μC/OS-II提供了函数OSIntEnter()和OSIntExit(),用于中断处理。函数OSIntEnter()通知操作系统进入中断服务程序,函数OSIntExit()在中断服务程序返回时进行相应的处理。μC/OS-II的中断响应过程如图2所示。进入中断服务程序时,首先将全部CPU寄存器存入当前任务栈,然后调用函数OSIntEnter(),或者将中断嵌套层数计数器,即全局变量OSIntNesting直接加1,通知μC/OS-II进入中断服务程序,执行用户代码进行中断服务。中断服务完成后调用函数OSIntExit(),将变量OSIntNesting减1。当OSIntNesting减到O时,所有中断执行完毕,此时μC/OS-II要判断是否有优先级较高的任务被中断服务程序唤醒。如果有优先级高的任务进入就绪态,μC/OS-II就返回到优先级高的任务执行;否则,返回到当前任务继续执行。

点击看原图

通过对μC/OS-II中断处理过程的分析可知,μC/OS-II只是提供了简单的中断管理机制,对于中断进入时的中断环境保护、中断退出时的中断环境恢复、中断嵌套处理和堆栈分配等问题没有给出具体的处理方法。另外,对于不同的处理器,其中断处理的方法也不一样,所以在不同的处理器上移植μC/OS-II后,要根据处理器的具体特点,进行中断系统的设计。

3 中断系统设计

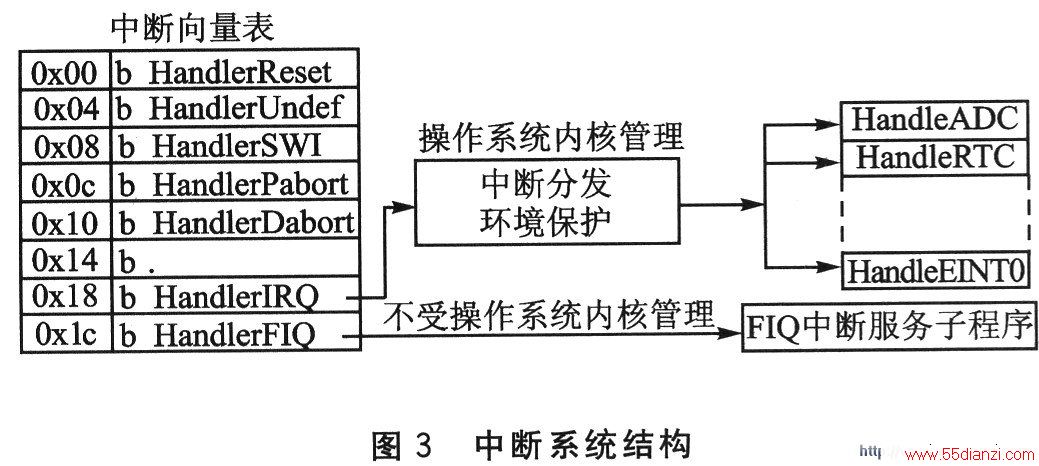

在中断系统设计过程中,所有的IRQ中断纳入操作系统的管理范围,由操作系统统一管理;FIQ中断独立于操作系统之外,不受操作系统管理。因此,中断系统的设计包括两部分:IRQ中断和FIQ中断。

3.1 中断系统结构

S3C44BOX提供了IRQ和FIQ两种中断方式。ARM中设计FIQ中断是为了在快速处理的场合使用,但是进入操作系统进行管理的任何中断都需做一些同样的前期准备工作和后期结束工作,包括为被中断的任务保存环境等。如果把FIQ中断纳入操作系统进行管理,则FIQ中断的优势并不明显,因此,在中断系统的设计过程中没有将FIQ中断纳入操作系统的管理范围,而是由用户单独进行FIQ中断服务程序的设计。

S3C4480X针对IRQ中断方式,提供了向量中断方式,这样在中断发生时可以减少中断程序的跳转次数,进而缩短中断响应时间;但是μC/OS-II移植到S3C44B0X处理器上之后,所有的IRQ中断都要由操作系统进行统一的管理,即在中断发生时程序都要跳转到统一的入口处进行中断环境保护,然后执行中断服务程序。如果采用向量中断,不但不能缩短中断的响应时间,反而在中断发生时由于程序要跳转到统一的入口处而延长中断的响应时间。

www.55dianzi.com

由上面的分析可知, 中断系统 的设计中没有将FIQ中断纳入操作系统的管理范围,而是由用户自己根据实际情况进行设计。一方面可以提供快速的中断反应,另一方面增强了系统的灵活性;同时,由于向量中断用于操作系统不能加快中断的反应速度,所以在中断系统的设计中也没有使用向量中断方式。中断系统的结构如图3所示。当发生IRQ中断时,处理器会从地址Ox18处取指令,执行0x18处的跳转指令,跳转到统一的中断人口,进行中断分发和环境保护后执行具体的中断服务程序。IRQ中断处理的过程由操作系统统一管理。与IRQ中断相比,FIQ中断处理过程比较简单,当发生FIQ中断时,处理器会执行地址0x20处的跳转指令直接转到具体的中断服务程序。

点击看原图

3.2 ARM 处理器运行模式

ARM处理器有7种运行模式:用户模式(USR)、系统模式(SYS)、管理模式(SVC)、中止模式(ABT)、未定义模式(UND)、普通中断模式(IRQ)和快速中断模式(FIQ)。处理器在不同的情况下处于不同的模式中。在中断系统的设计中,主要涉及SVC、UND、IRQ和FIQ四种模式。

在ARM处理器中,SVC模式通常是操作系统内核代码的运行模式,μC/OS-II内核中主要代码在SVC模式下运行,系统任务代码运行在SVC模式下。

IRQ/FIQ模式是在发生IRQ/FIQ中断后处理器强制进入的模式,用于中断处理。ARM处理器在发生IRQ/FIQ中断时自动改写IRQ/FIQ模式中的LR寄存器,LR保存被中断模式的返回地址(进入中断前的PC值),以便中断退出时能够正确返回到被中断模式;同时,LR也是每个模式下函数调用的返回地址寄存器。也就是说,LR寄存器具有保存函数返回地址和中断返回地址两种功能,LR的双重功能在中断嵌套程序设计中会发生冲突。

如果用IRQ/FIQ模式嵌套中断自身,则本模式的LR被改写后,本模式下原有的函数返回地址就无法还原。因此,应该在关闭中断的条件下,在IRQ/FIQ模式中进行基本的环境保护后,将中断服务程序切换到SYS模式下运行。这种处理方式能够保证产生中断嵌套时,被中断的模式是SYS模式而不是IRQ/FIQ模式自身,IRQ/FIQ模式中的LR保存着回到SYS模式的返回地址,SYS模式中的LR未被破坏,保存着函数返回地址。在移植中使用UND模式替代SYS模式作为中断服务的运行模式,这样可以实现中断嵌套的功能。

3.3 中断嵌套方式

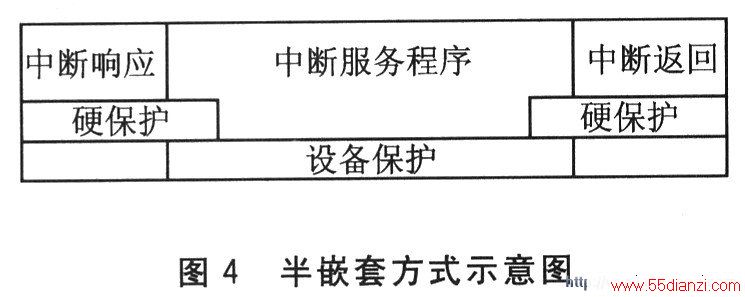

嵌套应该采用半嵌套方式,并不需要完全嵌套方式。“半嵌套”是指不同设备中断之间可以嵌套,但是同一设备中断不能嵌套。这样设计既照顾了系统实时性的要求,又能让系统具有更明确和稳定的行为;否则,如果开发完全嵌套,中断服务的堆栈空间就存在不确定性,甚至中断响应时间上限也存在不确定性,这些显然不能满足 嵌入式 实时系统的需求。

通过设置CPSR寄存器的中断屏蔽位F/I来屏蔽系统的中断,这样的保护称为“硬保护”;通过设置中断屏蔽寄存器中的相应位以屏蔽某一具体的中断,这样的保护称为“设备保护”。要实现半嵌套方式,需要在中断进入和退出时,在适当的时候进行两种保护方式的切换:

①在进入设备保护后还没有读取数据时退出硬保护。

②在即将退出ISR,使能设备中断位之前,再次恢复系统的硬保护。

具体的实现过程如图4所示。

本文关键字:暂无联系方式嵌入式系统-技术,单片机-工控设备 - 嵌入式系统-技术