采用QUARTus II软件对系统进行综合、仿真,系统在FPGA芯片中(EP2C70F672C6)实现。当采用50 MHz时钟处理图像大小为128×128×8的灰度图像时,背景更新和目标物体的提取所需时间大约为0.755 4 ms。由于采用流水线及并行处理操作方式,使其背景更新、目标提取和差分处理同步进行,加快了处理速度,从而完全能够保证图像系统的实时性。

4 实验验证

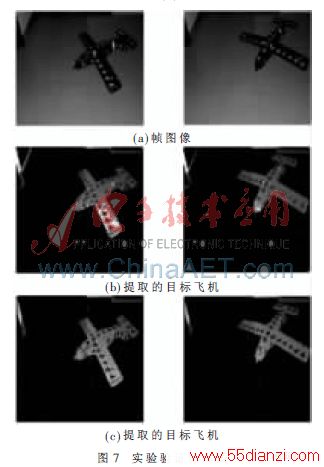

图7(a)为模型飞机在不同运动时刻不同姿态的帧图像;图7(b)为固定阈值背景更新、更新速率为0.875时所提取到的目标飞机;图7(c)为动态阈值背景更新、更新速率也为0.875时所提取到的目标飞机。可见动态阈值能更有效适应动态环境运动目标物体的提取。

本文针对改进型surendra背景更新算法原理的特点,结合硬件描述语言以及RAM存储器,提出了改进型surendra背景更新算法的硬件实现方案,并在FPGA芯片中实现了对运动目标物体的实时提取,提高了对运动目标物体的提取速度,同时也减少了系统资源的占用率,保证了系统的实时性要求。本方法在图像处理中有着广泛的应用前景。

参考文献

[1] HUANG Weiyao,LIU Zhijing,PAN Wenjuan.The precise recognition of moving object in complex background[C]. Third International Conference on Natural Computation,2007(2):246-252.

[2] 向海霞,王卫星.车辆检测中的自适应背景更新算法研究[J].计算机工程与应用,2009,45(11):235-237.

[3] 张彦,周忠,吴威.一种用于运动物体检测的自适应更新背景模型[J].计算机辅助设计与图形学学报,2008,20(10):1317-1321.

[4] 徐方明,卢官明.基于改进surendra背景更新算法的运动目标检测算法[J].山西电子技术,2009(5):39-40.

[5] 王绍雷,赵进创,周毅.基于FPGA的图像边缘检测系统的设计[J].电子技术应用,2007(6):40-42.

[6] 鲁恒.视频图像灰度信号直方图均衡的FPGA实现[J].电子技术应用,2006(11):105-107.

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术