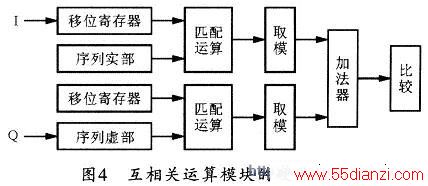

图4所示为互相关模块的FPGA实现框图,其中I、Q两路数据进入模块后,可取出其最高位存入移位寄存器,然后与本地序列做匹配运算。匹配运算模块由64个数据选择器和126个加法器组成,加法运算采用6级流水线来实现,这样,可使系统的运算速率更高。

4.3 仿真结果分析

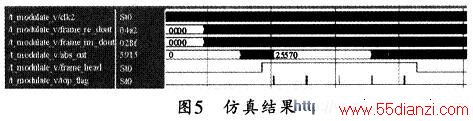

系统中的各模块可采用Verilog HDL语言设计,并可使用Xilinx公司集成设计环境 ISE 中的 ModelSim SE 6.0来完成仿真,仿真结果如图5所示。其中frame_re_dout和frame_im_dout为送入系统的实部和虚部数据,abs_out为延时自相关算法中取模相加的结果,frame_head为采用延时自相关算法使数据升高时得到的一个峰值平台,top_flag为改进自相关算法计算所得的峰值。图中的自相关平台内有5个峰值,这与MATLAB仿真结果相符。最后采用Xilinx公司VirtexⅡpro系列xc2vp30器件进行实现。总共逻辑单元使用率为8%,系统最高工作频率为236.373 MHz 。

5 结束语

本文在研究基于802.16d的OFDM定时同步算法的基础上提出了一种改进的算法,并在FPGA上完成了其硬件电路设计。仿真结果表明该算法在保持了原算法优秀性能的同时,可节省硬件资源,有利于把同步模块和接收部分其他模块集成在单芯片中。同时,该算法也可推广到具有相似前导字结构的802.1 1a等协议中。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术