比较正弦和反正切鉴相器的输出(图略),开始时输出误差较大,通过环路的调整,输出误差信号逐渐减小,最终趋于稳定。稳定后的输出最小值是鉴相器的最小分辨率,即为跟踪精度。跟踪精度除了和鉴相器本身特性有关,还和环路滤波器的参数设置有关。通过对比可知,利用正切鉴相器比正弦鉴相器实现跟踪速度快。

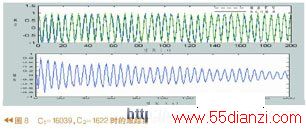

另外对环路滤波器取两组不同参数时环路的性能分别进行了仿真。数字环路滤波器在环路中对输入噪声起抑制作用,并且对环路的校正速度起调节作用。采用理想二阶环,设置C_{1}和C_{2},采用反正切鉴相器,仿真结果如图7、图8。图7是 C_{1}=1200、C_{2}=16时的环路的跟踪结果和鉴相器输出,图8是C_{1}=16039、 C_{2}=1622时环路的跟踪结果和鉴相器输出。横坐标为时间,纵坐标为信号幅度。从图7中可以看出,环路在10s左右即可以实现跟踪,相应的鉴相器的输出也很快维持在0值的附近。如图8,当C_{2}较大时,跟踪时间明显延长,鉴相器的输出波动很大。

环路测试

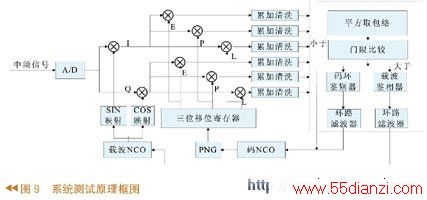

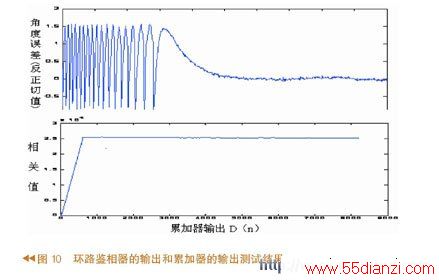

在系统测试中,测试原理如图9所示,在-5dB条件下,载波环带宽为40Hz,码环带宽为10Hz。对载波环路进行测试,载波环鉴相器及累加器的输出如图10所示。在稳定跟踪后,累加器的输出稳定在一个相对固定的数量级上。

结束语

科斯塔斯环由于对载波上的调制信息不敏感,在直扩 导航 数字接收机中被普遍采用。本环路设计已在一款测距接收机中得到应用,在一片 FPGA (EP1C12Q240C8)上编程实现。经测试,在系统可提供33dB的扩频增益的条件下,输入信噪比高于-30dB时,环路正常工作,在-5dB时,多普勒频移±2kHz条件下,经本载波跟踪环路后残余频差小于1Hz,残余相差小于3°。

本文关键字:导航系统 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:数字下变频的FPGA实现