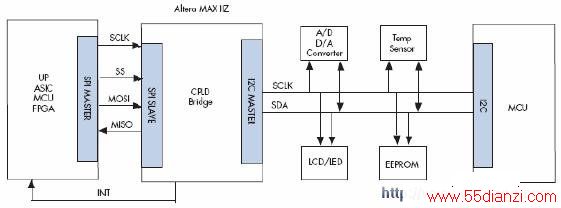

图6所示为采用CPLD来桥接两种不同的串口:I2C和SPI。这一设计可以在MAX IIZ EPM240Z CPLD中实现,使用了大约43%的逻辑和6个I/O引脚(4)。

图6. 利用MAX IIZ CPLD实现I2C至SPI接口

串行至并行转换

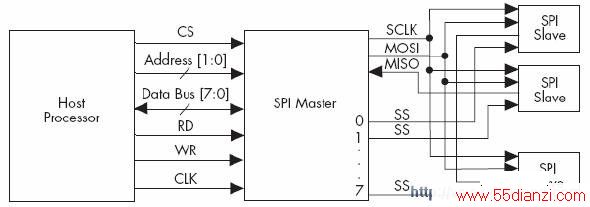

图7所示为主处理器和SPI主机的接口,使用CPLD来实现串并转换接口。这个例子建立一个主处理器总线接口和完整的SPI主机,可以在MAX IIZ EPM240Z CPLD中实现,占用了大约30%的逻辑和25个I/O引脚(5)。

点击看原图

图7. 利用MAX IIZ CPLD实现主处理器至SPI接口

并行至并行转换

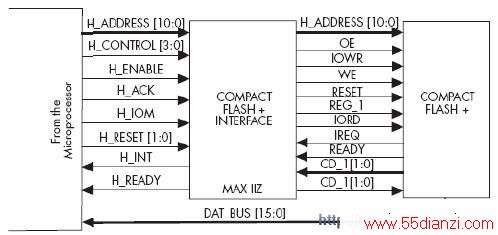

在图8中,CPLD被用于桥接两种不同的并口。这一实例实现了ComPACt FLASH+器件的主处理器总线接口,在MAX IIZEPM240Z CPLD中实现,使用了大约54%的逻辑,以及45个I/O引脚(6)。

图8. 利用MAX IIZ CPLD实现主处理器至CF+接口

传统上,某些微控制器一直是低功耗电子设计人员的唯一“可编程”逻辑选择。然而,随着低功耗CPLD的推出,设计人员在便携式应用上有了新的选择。本白皮书的多个实例介绍了怎样在便携式应用中使用低功耗CPLD来替代或者扩展以前在微控制器中实现的多种功能。结果,低功耗电子设计人员在便携式应用中拥有了另一套解决问题的工具,在设计创新产品时,能更好地选择最佳器件。

参考文献

1. AN 426:使用MAX II CPLD作为模拟键盘编码器: www. ALTEra .com/literature/an/an426.pdf

2. AN 491:利用Altera MAX II CPLD自动启动: www.altera.com/literature/an/an491.pdf

3. AN 494:在Altera MAX II CPLD中利用I2C总线接口实现GPIO引脚扩展: www.altera.com/literature/an/an494.pdf

4. AN 486:利用MAX II CPLD实现SPI至I2C转换: www.altera.com/literature/an/an486.pdf

5. AN 485:Altera MAX II CPLD中的串行外设接口(SPI)主机: www.altera.com/literature/an/an485.pdf

6. AN 492:利用Altera MAX II CPLD实现CF+接口: www.altera.com/literature/an/an492.pdf

详细信息

本文关键字:微处理器 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术