��������һ���Ƕ��ʽ����õ� FPGA �������� ������ ��FPGA������ִ���κν��������Զ���IP �������ܼ����㷨��������ͨ����ȡһЩ�������� FPGA���������ϵͳ���ܣ��Ӷ�ʹ��Ƭ���������ܼ����������ڳ�����ʱ�䡣FPGA���ṩ�����������ص��������ԣ�����Ӧ���ϱ仯�ı���

��������FPGA��MCU��������ֻ���ʵ�ַ�ʽ��һ������FPGA���ṹ������MCU���ˣ�һ����ʹ�û�����ɢFPGA�ı�MCU��Ʒ��FPGA����������Ч���������MCU��ȣ��÷�ʽʵ��һ���������DZȽϰ���ͺĵ�ġ�������ʹ�û���32λARM���ںˡ����������FPGA�������˵�FPGA MCU���ֻռ����֮һ�����������֮���ǻ�����ɢFPGA�ı���������Ʒ��

��������������Ʒ��FPGA��û����Ч�ķ�չ����֮���ͨ�ţ�����ʹ�ò�ͬ�����ԡ���ˣ�����֮��� �ӿ� ����һ����ս��FPGA��û���κ�ר�ŵ�����·����������ͨѶ�����ȣ�������ģ�����Ʊ�����㿪ʼ����Σ���������FPGA֮���ͨ�����첽�ġ��ر�����Ҫʹ��Ƭ����FPGAʱ����ͬ������������ǽӿڣ��������������ߣ�������ƿ�����⡣MCU��FPGA֮�����Ϣ����ͨ����Ҫ��MCU������ѭ������ͨ��ռ����Դ��PIO or EBI��Ӱ�촫���ٶȡ���˱���ע��������ⲿSRAM����������������ߵ�ƿ�����⡣

����MCU��FPGA�ӿڻ�����������Ӳ��ѡ�ɱ�̵�I / O��PIO�����ⲿ���߽ӿڣ� EBI�ģ�������еĻ������MCU֮���һ��ר�ŵĽӿڣ��Ƚ��ĸ������ߣ� AHB ����FPGA ���÷�����ʹ�������ڸ߶�Ӧ�ú��г�������

����PIO�ӿ�

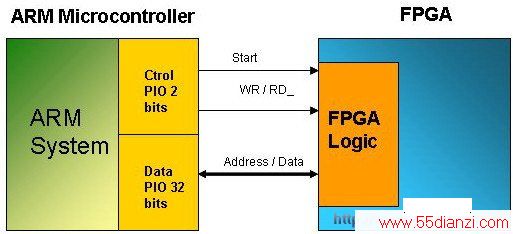

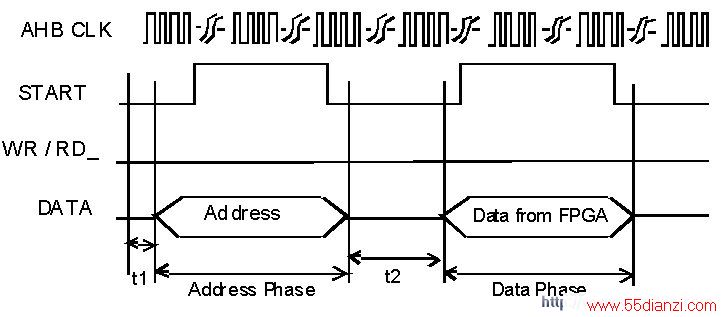

����ͨ��PIO ����MCU��FPGA��Լ����ݴ�����˵�Ƚϼ���������32λ�ĵ�ַ�� 32λ���ݣ�����һЩ�����źŵĿ��ơ������Ҫһ��32λ��PIO��һ��2λPIO��ͼ1�� ��

ͼ1 PIO����FPGA

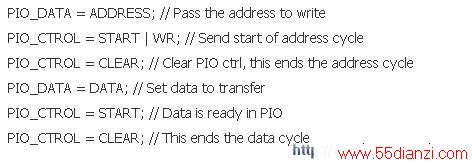

����Ϊ�˽����ݴ��䵽FPGA��PIO�е�˫���������������Ϊ��������ݴ��䵽FPGA�������㷨ʵ�����£�

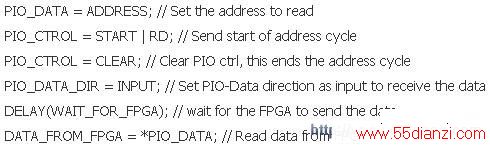

������FPGA��ȡ���ݵķ������ơ�ͬ����PIO�еĻ��������ȱ�������Ϊ�����Ȼ��ı䷽��Ϊ�����FPGA��ȡ���ݣ�������ִ�д��룺

���������㷨��һ�������Ĵ��䣬���Ƚ����㷨�DZ�Ҫ��ARM��������FPGA֮�佨���ʵ���ͨ�š��ر�Ҫע����ǣ�ȷ�����ݵĿɿ��ԣ�����û������ٻ�ȴ��������������ʧ�ȡ�

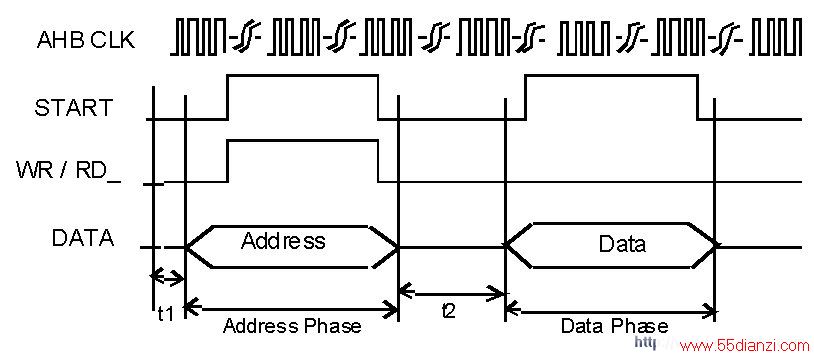

��������ʱ�������ܺͣ�

T����-PIO=t1+������+t2+���ݽ�

����ʹ������Ż���GCC��������ϵͳ��Լ��Ҫ55��AHB������FPGAִ��д������ͼ2����

�����ԭͼ

ͼ2 PIO��FPGA д����

��������t2��FPGA�ĵȴ���Ӧʱ�䣩Ҳ��Լ��25�� AHB���ڣ�ϵͳ��Լ��Ҫ85��AHB���ڴ�FPGA���ж�������ͼ3����

�����ԭͼ

ͼ3 PIO��FPGA��ȡ����

����MCU�����ӿ����ӷdz���ֱ���˵���Ȼ������FPGA�����������������������е���PIO���ɵ�ҵ�������ڴ��������£���������ҵ��������ȫ�첽����ˣ�FPGA�����ܹ����������й����������źţ�����FPGA������ʱ�䴰����ҵ�������������յ���FPGA�ڡ�

������Ϊ������ר�Ÿ���ά��PIO���������Դ���ʱ�����ĺܴ���ȻCPU�Ǵ������ݴ��䣬�����Dz�����������ˡ���ˣ���һ��������п���ʹϵͳ��������̱����DMA������ʹ�õ�PIO�ӿڣ����Գ���Ա�������Ƶ����ݴ������Ա����������ܹ���MCU����ͨѶ�����磬�����һ������Ľ���Ҫ��100 ���Ĵ������������ڣ�ͬʱ��Ҫ��FPGA���д��У�SPI��USART��TWI��ͨ�ţ�����д������ô���������̱�����һ��Ҫ�ȴ���������͵����������FPGA������û�м�ʱ�Ĵ������������ô����һ���ֽ�/������ʱ���ܻ�������ӱ����Ͻ���Ƕ��ʽ��������Ϊ��ߔ���������ƶ�Ӳ�̡�

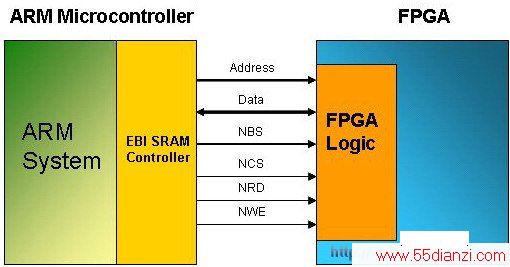

����ͨ���ⲿ���߽ӿ����ӣ� EIB ��

��������32λ��������һ���ⲿ���߽ӿڣ�EBI��ģ�飬����Ϊ�ⲿ�豸�ͻ���ARM�豸�Ĵ洢������֮�䴫�����ݶ���Ƶġ���Щ�ⲿ�洢�������ܹ������������͵��ⲿ�洢������Χ�豸����SRAM��PROM��EPROM��EEPROM��flash��SDRAM��ֻҪFPGA���Դ���Ԥ����洢���ӿڣ�EBIҲ������FPGA�Ľӿڡ���EBI��ʹ�þ�̬�洢���ӿڣ�SRAM������FPGAͨ����˵����õģ���Ϊ����Ƽ��Ҵ��������߶���Ϥ��������PIO�ӿڣ� FPGA���ò�����һ��ģ�飬��������SRAMʱ�䣬���ܲ���һ����Ӧ������������ͼ4����

ͼ4 EBI-SMC�ӿ�

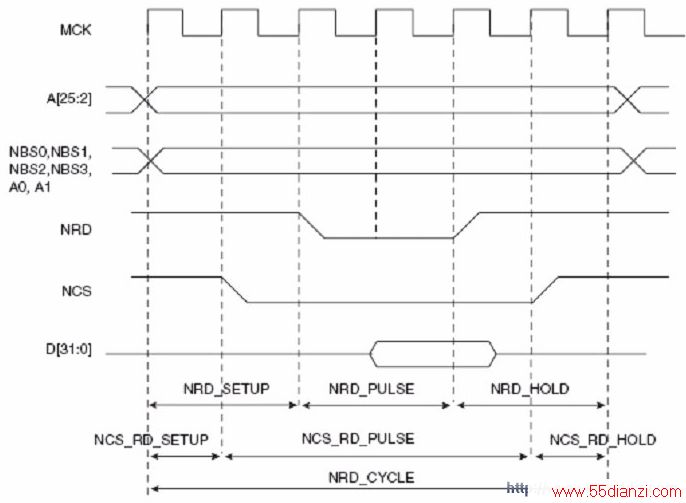

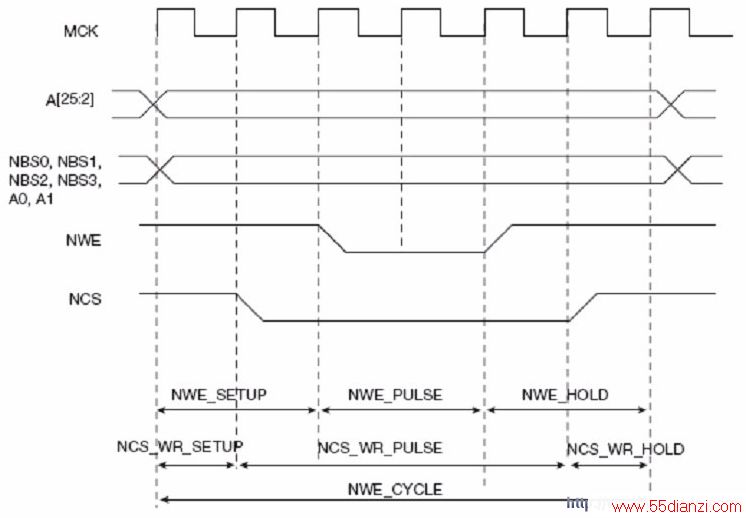

����ͼ5��ʾ��EBI��SMC�洢���ӿڵı�ʱ�䣬��ͼ6��ʾ�����д���ڡ�

�����ԭͼ

ͼ5 EBI-SMC������

�����ԭͼ

ͼ6 EBI-SMCд����

����ע�⣺��Щʱ�䲨����Ĭ�ϵ�SMC������пɱ�̲�����ʾ�������ⲿ�豸���ٶȡ�

����EBI�Ľӿ��ٶȱ�PIO�飬����ΪEBI�����Լ���I / O���Ҵֵ��ź��Dz��еġ����ǣ�����ⲿ�豸����������ȴ�״̬�� EBI���ٶ����ƿ��ܻ��ܵ���

������PIO�ӿ�һ���� EBI�ӿڱ����ɴ���������������AHB����������ˣ�ʵ�ִ�����EBI�Ļ���������������ȡ�������������ö��ٴ�����ʱ�䡣��Ȼ�������ܵ����������ơ����ֿ���������Ƕ��ʽ������ּ��ʵ�ֵ�����ϵͳ���ܡ�

������MCU��ʹ��ר�õ� FPGA �ӿ�

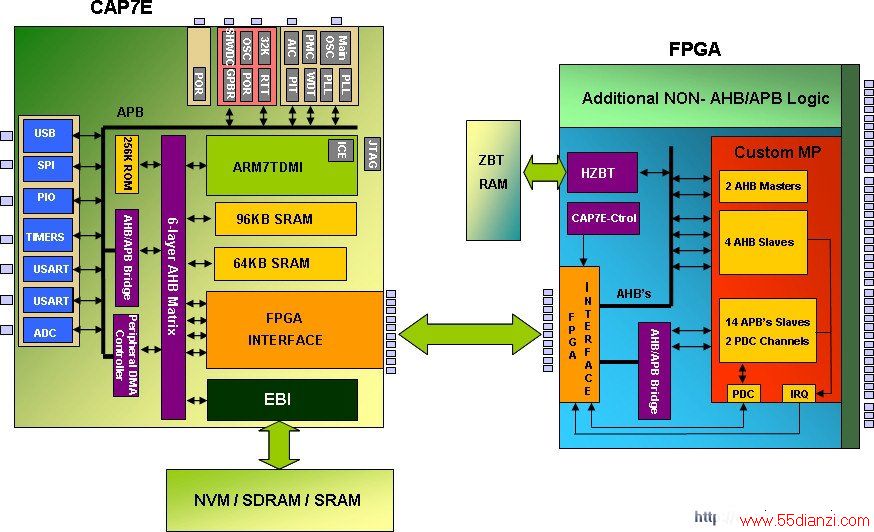

�������� ARM7 �� ������ �ṩһ������ӿڣ�������FPGAͨ��DMA��ȡ2����AHB���ĸ���AHBֱ�ӽ���MCU���ڲ�AHB���ߡ�������ʱ��һ����ӵĸ�AHB����������ӳ��ROM����ͨ��ʹ���ⲿZBT RAM����PROM����ӳ�书�ܵ�FPGA��ʵ�֡�

�����ýӿڻ��ṩ��FPGA����14�����Ƚ���Χ���ߣ�APB��������ȫ˫����DMAͨ�������13���ж����ȱ��루IRQs��������DMA����ķDZ���IRQs��32λ�����ɱ��I/O����FPGA�ӿ�ͨ������������Ԥ�ȶ��������AHB��ͼ7����

�����ԭͼ

ͼ7 MCUר�õ�FPGA�ӿ�

����FPGA�ӿ��ǻ��ڶ��������ת����������ͽ���������������FPGA֮���ҵ������Ϊ��ʹ������ͬ�豸֮���ܽ�����Ч��ͬ��ͨ�ţ�������������Ҫ��

������FPGA�����ܹ�����ʱ��ƫбƽ���ʱ������������˼��FPGA����DCM������ʱ�ӹ�������ǿ���Դ�������ʱ����������Ҫ�����ʱ�ӡ�ALTEra��������Ҫʹ�������·����FPGA������Ϊ�����������ýӿ��ṩ���ú�λ��ʽ��������Ϊ�������ṩ�Ĵ���ͨ��ʱ�ӣ�Ƶ�ʷ�ΧӦ��100�����ϡ�ARM7���ڲ�ʱ�Ӻʹ���ʱ��֮��ı���ӦΪ0.8����ͣ�ARM��ʱ��/����ʱ�ӣ���

���Ĺؼ��֣���� ������ �ӿ� DSP/FPGA��������Ƭ��-�����豸 - DSP/FPGA����